120

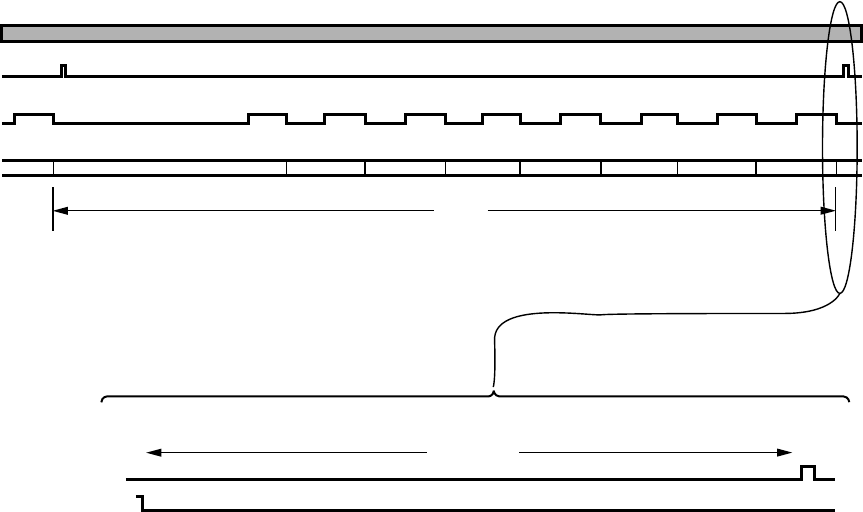

Figure 43. Transmit Overhead Clock and Data Alignment

The transmit overhead clock and data alignment timing diagram (Figure 43) shows the relationship

between the TX_E1_DATA, TX_E2_DATA and TX_F1_DATA serial data inputs and their associated clock

TX_E1E2F1_CLK. It is a 72 kHz 50% duty cycle clock that is gapped to produce a 64 kHz nominal rate

and is aligned as shown.

TX_FRAME_SFP

TX_E1E2F1_CLK

TX_E1_DATA

TX_SONETCLK

E1, F1, E2

APPROX. 750 ns

B1 B2

B3 B4 B5 B6 B7 B8

TX_FRAME_SFP

TX_E1E2F1_CLK