High Speed Converter Evaluation Platform

HSC-ADC-EVALC

Rev. 0

Evaluation boards are only intended for device evaluation and not for production purposes.

Evaluation boards as supplied “as is” and without warranties of any kind, express, implied, or

statutory including, but not limited to, any implied warranty of merchantability or fitness for a

particular purpose. No license is granted by implication or otherwise under any patents or other

intellectual property by application or use of evaluation boards. Information furnished by Analog

Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog

Devices for its use, nor for any infringements of patents or other rights of third parties that may result

from its use. Analog Devices reserves the right to change devices or specifications at any time

without notice. Trademarks and registered trademarks are the property of their respective owners.

Evaluation boards are not authorized to be used in life support devices or systems.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 ©2007 Analog Devices, Inc. All rights reserved.

FEATURES

Xilinx Virtex-4 FPGA-based buffer memory board

Used for capturing digital data from high speed ADC

evaluation boards to simplify evaluation

64 kB FIFO depth

Parallel input at 644 MSPS SDR and 800 MSPS DDR

Supports 1.8 V, 2.5 V, and 3.3 V CMOS and LVDS interfaces

Supports multiple ADC channels up to 18 bits

Measures performance with VisualAnalog

Real-time FFT and time domain analysis

Analyzes SNR, SINAD, SFDR, and harmonics

Simple USB port interface (2.0)

Supports ADCs with serial port interfaces (SPI)

FPGA reconfigurable via JTAG, on-board EPROM, or USB

On-board regulator circuit speeds setup

5 V, 3 A switching power supply included

Compatible with Windows 98 (2nd edition), Windows 2000,

Windows ME, and Windows XP

EQUIPMENT NEEDED

Analog signal source and antialiasing filter

Low jitter clock source

High speed ADC evaluation board and ADC data sheet

PC running Windows 98 (2nd edition), Windows 2000,

Windows ME, or Windows XP

Latest version of VisualAnalog

USB 2.0 port recommended (USB 1.1 compatible)

PRODUCT HIGHLIGHTS

1. Easy to Set Up. Connect the included power supply along

with the CLK and AIN signal sources to the two evaluation

boards. Then connect to the PC via the USB port and

evaluate the performance instantly.

2. USB Port Connection to PC. PC interface is via a USB 2.0

connection (1.1 compatible) to the PC. A USB cable is

provided in the kit.

3. 64 kB FIFO. The on-board FPGA contains an integrated

FIFO to store data captured from the ADC for subsequent

processing.

4. Up to 644 MSPS SDR/800 MSPS DDR Encode Rates on

Each Channel. Multichannel ADCs with encode rates up

to 644 MSPS SDR and 800 MSPS DDR can be used with

the ADC capture board.

5. Supports ADCs with Serial Port Interface or SPI. Some

ADCs include a feature set that can be changed via the

SPI. The ADC capture board supports these SPI-driven

features through the existing USB connection to the

computer without additional cabling needed.

6. VisualAnalog™. VisualAnalog supports the HSC-ADC-

EVALC hardware platform as well as enabling virtual ADC

evaluation using ADIsimADC™, Analog Devices proprietary

behavioral modeling technology. This allows rapid compari-

son between multiple ADCs, with or without hardware

evaluation boards. For more information, see AN-737 at

www.analog.com/VisualAnalog.

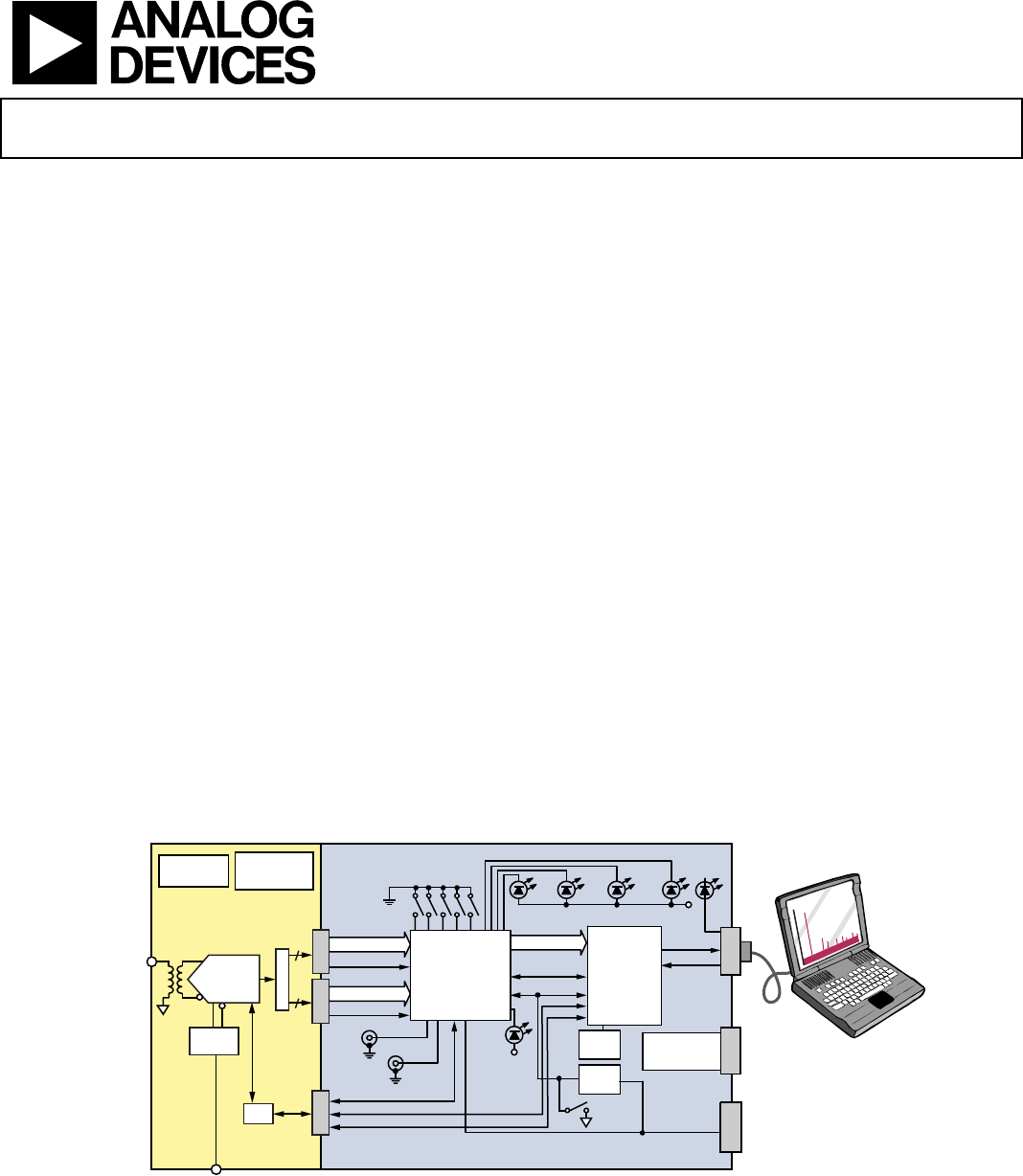

FUNCTIONAL BLOCK DIAGRAM

06676-001

FPGA

CONFIGURATION

MODE

EXT SYNC2

LED2 LED1

FIFO

CONTROL(9)

J1*

J2*

J3*

J10

RECONFIG

DATA(16)

EXT SYNC1

*DATA CONVERTER I/O CONNECTORS

DATA BUS 1(18)

CLKB(2)

FPGA GPIO(8)

SPI(7)

USB DIRECT(5)

DATA BUS 2(18)

CLKA(2)

FPGA

DONE

FPGA

CONFIG

PROM

USB

CONFIG

PROM

JTAG

CONNECTOR

POWER

CONNECTOR

USB

CONNECTOR

USB

CONTROLLER

CAPTUREUPLOAD

PORTC

PORTB

PORTD

PORTE

PORTA

ONBOARD

VOLTAGE

REGULATORS

J4

CLOCK INPUT

FILTERED

ANALOG

INPUT

LOGIC

SPI

ADC

n

n

J6

USB

STANDARD

USB 2.0

ON-BOARD

VOLTAGE

REGULATORS

POWER

CONNECTOR

FPGA

SINGLE OR MULTICHANNEL

HIGH SPEEDADC

EVALUATION BOARD

HSC-ADC-EVALC

CLOCK

CIRCUIT

Figure 1.