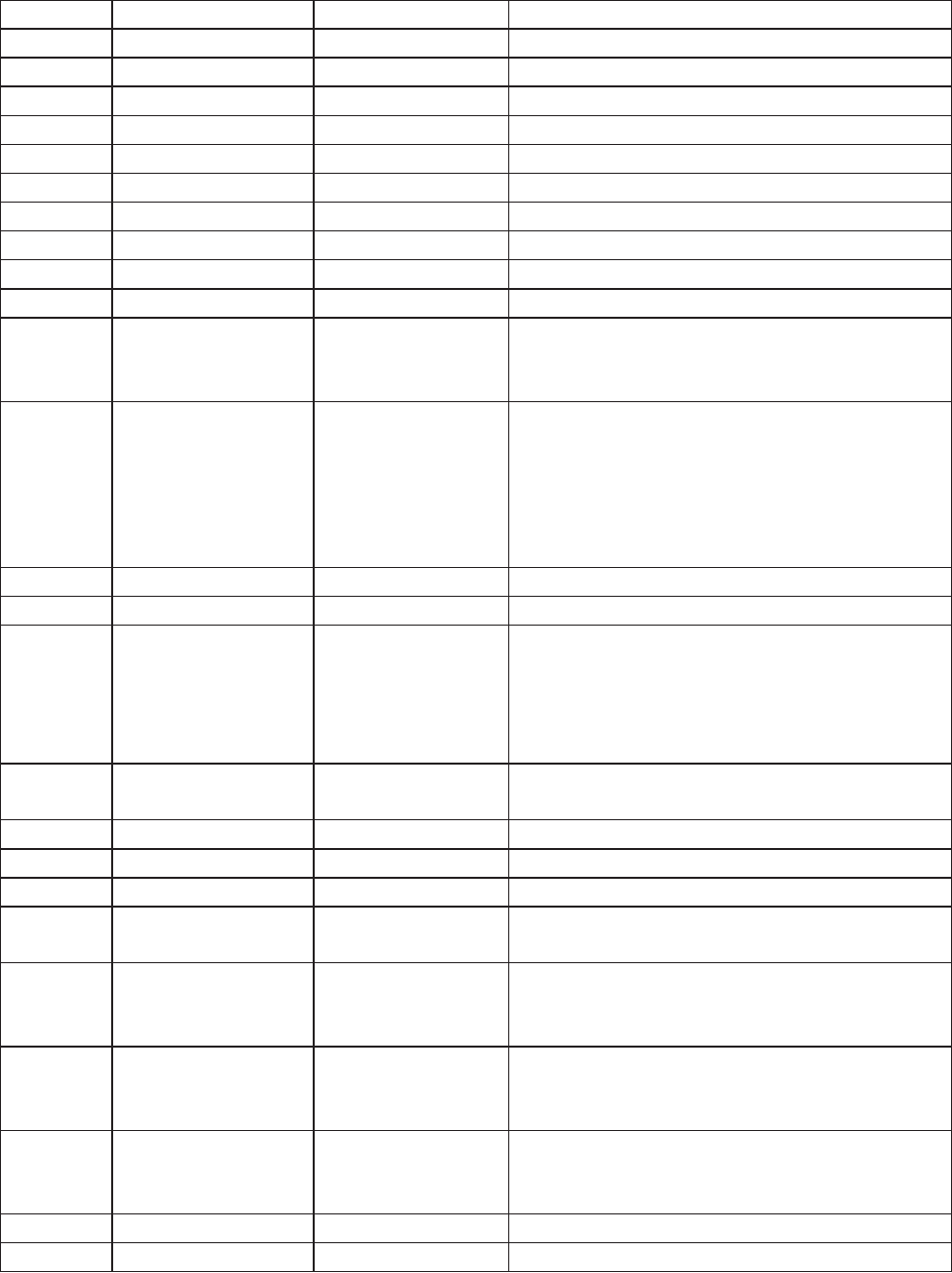

84

Location Mnemonic Type Description

87 AP0_OUT Digital Output Audio output port 0.

88 AP1_OUT Digital Output Audio output port 1.

89 AP2_OUT Digital Output Audio output port 2.

90 AP3_OUT Digital Output Audio output port 3.

91 AP4_OUT Digital Output Audio output port 4.

92 DGND Ground Ground for DVDD

93 DVDD Power Digital supply voltage (1.8 V)

94 AP5_OUT Digital Output Audio output port 5.

95 SCLK_OUT Digital Output Audio serial clock output.

96 MCLK_OUT Digital Output Audio master clock output.

97 RESETB Digital Input System reset input. Active low. A minimum

low reset pulse width of 5 ms is required to

reset the ADV7622 circuitry.

98 PWRDNB Digital Input Active low power-down pin. This pin

should be used as a system detect when the

internal EDID is powered from the 5V

signal from the HDMI port when connected

to active equipment. Pin pulled down

internally.

99 PGND Ground Ground for PVDD

100 PVDD Power PLL supply voltage

101 XTAL Miscellaneous

Analog

Input pin for 28.63636 MHz crystal or an

external 1.8 V 28.63636 MHz clock

oscillator source to clock the ADV7622.

The following crystal frequencies are also

supported: 24.576 MHz and 27 MHz.

102 XTAL1 Miscellaneous

Analog

Crystal output pin. This pin should be left

floating if a clock oscillator is used.

103 PVDD Power PLL supply voltage

104 PGND Ground PVDD Ground

105 HP_CTRLA Digital Output Hot Plug Detect for port A.

106 5V_DETA Digital Input 5 V detect pin for port A in the HDMI

interface.

107 RTERM Miscellaneous

Analog

Sets internal termination resistance. A 500

Ω resistor between this pin and GND

should be used.

108 DDCA_SDA Digital I/O HDCP slave serial data port A.

DDCD_SDA is a 3.3 V input/output that is

5 V tolerant.

109 DDCA_SCL Digital Input HDCP slave serial clock port A.

DDCD_SCL is a 3.3 V input that is 5 V

tolerant.

110 CVDD Power Receiver comparator supply voltage (1.8V)

111 CGND Ground TVDD and CVDD Ground