THE SYMBOL MARK OF THIS SCHEMETIC DIAGRAM INCORPORATES

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

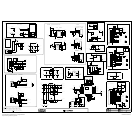

BRA[2]

ARDQ[23]

BRDQ[5]

BRDQ[9]

ARDQ[0]

BRDQ[6]

ARDQ[16]

ARDQ[9]

BRA[15]

ARDQ[24]

ARA[4]

BRA[4]

ARDQ[22]

ARA[14]

ARDQ[2]

BRA[0]

BRA[9]

BRDQ[2]

ARDQ[5]

ARDQ[12]

BRA[7]

BRA[13]

ARA[3]

BRDQ[8]

ARDQ[17]

BRDQ[4]

ARA[6]

ARDQ[11]

ARA[10]

BRDQ[14]

BRDQ[13]

ARA[9]

ARDQ[25]

BRA[6]

ARDQ[7]

BRDQ[0]

ARDQ[1]

ARA[7]

ARDQ[31]

BRA[3]

ARDQ[18]

BRDQ[7]

ARDQ[10]

ARDQ[8]

ARA[8]

ARA[12]

BRDQ[15]

BRDQ[3]

ARDQ[6]

ARDQ[26]

ARA[1]

ARDQ[27]

ARDQ[19]

BRDQ[12]

ARA[0]

ARDQ[20]

ARDQ[28]

ARDQ[14]

BRA[1]

ARA[11]

BRDQ[1]

BRA[8]

BRA[10]

ARDQ[30]

ARDQ[29]

BRDQ[10]

BRDQ[11]

BRA[14]

ARDQ[15]

ARDQ[3]

ARDQ[4]

ARDQ[13]

BRA[11]

BRA[5]

BRA[12]

ARA[5]

ARDQ[21]

ARA[13]

ARA[2]

ARA[0]

ARDQ[21]

ARDQ[1]

ARDQ[27]

ARDQ[26]

ARDQ[2]

ARDQ[22]

ARA[6]

ARDQ[20]

ARDQ[6]

ARA[1]

ARDQ[23]

ARDQ[9]

ARDQ[7]

ARA[4]

ARA[8]

ARA[13]

ARA[2]

ARDQ[4]

ARDQ[28]

ARDQ[16]

ARDQ[10]

ARDQ[30]

ARA[8]

ARA[5]

ARA[11]

ARDQ[18]

ARA[10]

ARA[6]

ARDQ[13]

ARA[5]

ARA[3]

ARA[9]

ARA[3]

ARDQ[25]

ARA[2]

ARDQ[24]

ARDQ[3]

ARA[4]

ARA[13]

ARDQ[29]

ARA[7]

ARA[7]

ARDQ[12]

ARDQ[0]

ARDQ[14]

ARA[12]

ARDQ[11]

ARA[1]

ARDQ[17]

ARDQ[31]

ARDQ[15]

ARA[12]

ARA[10]

ARA[11]

ARDQ[19]

ARA[0]

ARDQ[5]

ARA[9]

ARA[14]

ARA[14]

ARDQ[8]

BRA[1]

BRA[8]

BRDQ[11]

BRA[2]

BRA[11]

BRDQ[13]

BRDQ[2]

BRDQ[8]

BRDQ[4]

BRDQ[12]

BRDQ[9]

BRA[13]

BRDQ[15]

BRDQ[3]

BRA[7]

BRDQ[1]

BRDQ[14]

BRDQ[5]

BRA[6]

BRA[3]

BRA[5]

BRDQ[6]

BRA[10]

BRA[4]

BRA[12]

BRA[9]

BRDQ[0]

BRA[0]

BRDQ[10]

BRDQ[7]

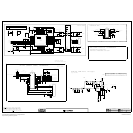

CI_ADDR[4]

CI_ADDR[13]

CI_DATA[6]

CI_ADDR[0]

CI_DATA[0]

CI_ADDR[9]

CI_ADDR[8]

MT5398_TS_OUT[2]

MT5398_TS_OUT[7]

CI_DATA[5]

CI_DATA[7]

MT5398_TS_OUT[6]

MT5398_TS_OUT[3]

CI_DATA[1]

MT5398_TS_OUT[1]

CI_ADDR[10]

CI_ADDR[14]

CI_DATA[2]

CI_ADDR[7]

CI_ADDR[3]

CI_DATA[4]

MT5398_TS_OUT[5]

CI_ADDR[6]

MT5398_TS_OUT[4]

CI_ADDR[1]

CI_ADDR[12]

CI_DATA[3]

CI_ADDR[5]

CI_ADDR[2]

MT5398_TS_OUT[0]

CI_ADDR[11]

+1.2V_MTK_CORE

VDD3V3

+1.5V_DDR

VDD3V3

+1.2V_MTK_CORE

+1.5V_DDR

+3.3V_NORMAL

VDD3V3

+1.2V_MTK_CORE

3.3V_EMMC

+1.2V_MTK_CORE

TP501

+1.2V_MTK_AVDD

POWER_ON/OFF1

+1.2V_MTK_CORE

LAN_JACK_POWER

VDD3V3

+3.3V_NORMAL

TP500

AVDD_33SB

+3.5V_ST_WAKE

/ARCAS

ARBA1

/ARDQS1

/ARDQS3

+1.5V_DDR

/ARWE

/ARCLK0

ARDQS0

BRDQM1

BRBA0

/BRCLK0

RVREF_A

BRDQM0

/ARDQS0

+1.5V_DDR

ARCLK1

RVREF_C

/ARCLK1

/ARCS

/ARRAS

BRCKE

ARDQS3

/BRCAS

ARA[0-14]

RVREF_C

/BRRAS

ARDQ[0-7]

BRODT

ARDQ[8-15]

ARDQM3

ARDQS2

ARBA0

BRDQ[8-15]

+1.5V_DDR

BRDQ[0-7]

RVREF_A

BRCLK0

ARDQM2

ARDQ[24-31]

BRREST

/ARCSX

BRDQS1

BRA[0-15]

BRDQS0

ARBA2

BRBA1

+1.5V_DDR

/BRCS /BRDQS1

/BRWE

ARCLK0

ARCKE

ARODT

ARREST

BRBA2

/ARDQS2

ARDQM1

ARDQS1

/BRDQS0

VDD3V3

ARDQ[16-23]

ARDQM0

ARDQS3

A_RVREF4

ARDQM3

ARDQ[24-31]

/ARCAS

/ARDQS1

ARBA1

A_RVREF4

A_RVREF3

/ARCS

/ARCLK0

A_RVREF2

/ARDQS0

A_RVREF1

A_RVREF3

ARBA0

ARBA1

ARA[0-14]

+1.5V_DDR

ARODT

ARCKE

ARA[0-14]

+1.5V_DDR

/ARCAS

/ARCSX

+1.5V_DDR

ARBA2

A_RVREF1

ARDQM2

ARODT

ARDQ[8-15]

+1.5V_DDR

/ARDQS3

ARDQS1

+1.5V_DDR

ARDQ[16-23]

ARBA0

/ARDQS2

/ARWE

ARCLK0

ARDQM0

/ARRAS

ARREST

ARDQ[0-7]

ARBA2

ARDQS2

ARDQS0

/ARWE

ARCKE

/ARCLK1

ARCLK1

ARDQM1

+1.5V_DDR

/ARRAS

A_RVREF2

ARREST

BRDQS1

+1.5V_DDR

BRBA2

B_RVREF5

B_RVREF6

BRDQM1

BRDQM0

/BRCS

B_RVREF6

+1.5V_DDR

/BRDQS0

/BRRAS

/BRWE

BRA[14]

/BRDQS1

BRA[0-14]

BRCLK0

BRDQ[0-7]

+1.5V_DDR

/BRCLK0

BRODT

B_RVREF5

BRA[15]

BRREST

BRBA0

BRCKE

BRDQS0

BRDQ[8-15]

BRBA1

/BRCAS

+1.5V_DDR

+1.5V_DDR

+1.5V_DDR

+1.5V_DDR

/CI_CD2

MT5398_TS_IN[2]

SC_COM_SOC

/PCM_REG

TP308

TP354

TP335

TP311

MT5398_TS_IN[5]

TP309

TP310

/PCM_WAIT

/PCM_IOWR

TP314

TP307

/PCM_OE

MT5398_TS_IN[3]

PCM_5V_CTL

TP349

TP325

TP355

TP361

TP378

TP341

TP316

SC_FB_SOC

TP347

TP331

SCART_Rout_SOC

TP366

TP339

TP375

TP334

TP357

TP372

TP327

TP332

TP362

TP358

TP352

SC_R_IN_SOC

CI_A_VS1

MT5398_TS_IN[4]

MT5398_TS_OUT[0-7]

TP338

MT5398_TS_CLK

TP328

SC_ID_SOC

TP344

TP350

MT5398_MIVAL_ERR

TP326

/PCM_IRQA

TP345

TP321

SC_R_SOC

SC_CVBS_IN_SOC

TP317

MT5398_MCLKI

TP324

TP373

TP340

TP371

PCM_RST

/PCM_CE1

SC_G_SOC

MT5398_TS_SYNC

MT5398_TS_IN[6]

TP313

TP346

SC_DET

/CI_CD1

TP342

CI_ADDR[0-14]

TP318

/PCM_IORD

/PCM_WE

TP356

TP374

DTV/MNT_V_OUT_SOC

TP363

CI_DATA[0-7]

TP377

TP323

TP365

TP320

TP343

TP330

TP333

TP367

TP360

MT5398_TS_IN[7]

TP353

MT5398_TS_VAL

MT5398_TS_IN[0]

TP319

SC_B_SOC

TP364

TP337

TP336

MT5398_MISTRT

TP348

TP312

SC_L_IN_SOC

TP368

MT5398_TS_IN[1]

SCART_Lout_SOC

TP369

TP351

TP370

TP329

TP359

TP322

TP315

WOL_CTL

+3.5V_ST_WAKE

+3.5V_ST

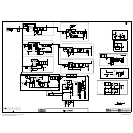

K4B2G1646E-BCK0

IC702-*1

DDR_256M_SS

A0

N3

A1

P7

A2

P3

A3

N2

A4

P8

A5

P2

A6

R8

A7

R2

A8

T8

A9

R3

A10/AP

L7

A11

R7

A12/BC

N7

A13

T3

NC_5

M7

BA0

M2

BA1

N8

BA2

M3

CK

J7

CK

K7

CKE

K9

CS

L2

ODT

K1

RAS

J3

CAS

K3

WE

L3

RESET

T2

DQSL

F3

DQSL

G3

DQSU

C7

DQSU

B7

DML

E7

DMU

D3

DQL0

E3

DQL1

F7

DQL2

F2

DQL3

F8

DQL4

H3

DQL5

H8

DQL6

G2

DQL7

H7

DQU0

D7

DQU1

C3

DQU2

C8

DQU3

C2

DQU4

A7

DQU5

A2

DQU6

B8

DQU7

A3

VREFCA

M8

VREFDQ

H1

ZQ

L8

VDD_1

B2

VDD_2

D9

VDD_3

G7

VDD_4

K2

VDD_5

K8

VDD_6

N1

VDD_7

N9

VDD_8

R1

VDD_9

R9

VDDQ_1

A1

VDDQ_2

A8

VDDQ_3

C1

VDDQ_4

C9

VDDQ_5

D2

VDDQ_6

E9

VDDQ_7

F1

VDDQ_8

H2

VDDQ_9

H9

NC_1

J1

NC_2

J9

NC_3

L1

NC_4

L9

NC_6

T7

VSS_1

A9

VSS_2

B3

VSS_3

E1

VSS_4

G8

VSS_5

J2

VSS_6

J8

VSS_7

M1

VSS_8

M9

VSS_9

P1

VSS_10

P9

VSS_11

T1

VSS_12

T9

VSSQ_1

B1

VSSQ_2

B9

VSSQ_3

D1

VSSQ_4

D8

VSSQ_5

E2

VSSQ_6

E8

VSSQ_7

F9

VSSQ_8

G1

VSSQ_9

G9

H5TQ4G63AFR-PBC

IC701-*1

DDR_512M_HYNIX

A0

N3

A1

P7

A2

P3

A3

N2

A4

P8

A5

P2

A6

R8

A7

R2

A8

T8

A9

R3

A10/AP

L7

A11

R7

A12/BC

N7

A13

T3

A15

M7

BA0

M2

BA1

N8

BA2

M3

CK

J7

CK

K7

CKE

K9

CS

L2

ODT

K1

RAS

J3

CAS

K3

WE

L3

RESET

T2

DQSL

F3

DQSL

G3

DQSU

C7

DQSU

B7

DML

E7

DMU

D3

DQL0

E3

DQL1

F7

DQL2

F2

DQL3

F8

DQL4

H3

DQL5

H8

DQL6

G2

DQL7

H7

DQU0

D7

DQU1

C3

DQU2

C8

DQU3

C2

DQU4

A7

DQU5

A2

DQU6

B8

DQU7

A3

VREFCA

M8

VREFDQ

H1

ZQ

L8

VDD_1

B2

VDD_2

D9

VDD_3

G7

VDD_4

K2

VDD_5

K8

VDD_6

N1

VDD_7

N9

VDD_8

R1

VDD_9

R9

VDDQ_1

A1

VDDQ_2

A8

VDDQ_3

C1

VDDQ_4

C9

VDDQ_5

D2

VDDQ_6

E9

VDDQ_7

F1

VDDQ_8

H2

VDDQ_9

H9

NC_1

J1

NC_2

J9

NC_3

L1

NC_4

L9

A14

T7

VSS_1

A9

VSS_2

B3

VSS_3

E1

VSS_4

G8

VSS_5

J2

VSS_6

J8

VSS_7

M1

VSS_8

M9

VSS_9

P1

VSS_10

P9

VSS_11

T1

VSS_12

T9

VSSQ_1

B1

VSSQ_2

B9

VSSQ_3

D1

VSSQ_4

D8

VSSQ_5

E2

VSSQ_6

E8

VSSQ_7

F9

VSSQ_8

G1

VSSQ_9

G9

H5TQ4G63AFR-PBC

IC703-*1

DDR_512M_HYNIX

A0

N3

A1

P7

A2

P3

A3

N2

A4

P8

A5

P2

A6

R8

A7

R2

A8

T8

A9

R3

A10/AP

L7

A11

R7

A12/BC

N7

A13

T3

A15

M7

BA0

M2

BA1

N8

BA2

M3

CK

J7

CK

K7

CKE

K9

CS

L2

ODT

K1

RAS

J3

CAS

K3

WE

L3

RESET

T2

DQSL

F3

DQSL

G3

DQSU

C7

DQSU

B7

DML

E7

DMU

D3

DQL0

E3

DQL1

F7

DQL2

F2

DQL3

F8

DQL4

H3

DQL5

H8

DQL6

G2

DQL7

H7

DQU0

D7

DQU1

C3

DQU2

C8

DQU3

C2

DQU4

A7

DQU5

A2

DQU6

B8

DQU7

A3

VREFCA

M8

VREFDQ

H1

ZQ

L8

VDD_1

B2

VDD_2

D9

VDD_3

G7

VDD_4

K2

VDD_5

K8

VDD_6

N1

VDD_7

N9

VDD_8

R1

VDD_9

R9

VDDQ_1

A1

VDDQ_2

A8

VDDQ_3

C1

VDDQ_4

C9

VDDQ_5

D2

VDDQ_6

E9

VDDQ_7

F1

VDDQ_8

H2

VDDQ_9

H9

NC_1

J1

NC_2

J9

NC_3

L1

NC_4

L9

A14

T7

VSS_1

A9

VSS_2

B3

VSS_3

E1

VSS_4

G8

VSS_5

J2

VSS_6

J8

VSS_7

M1

VSS_8

M9

VSS_9

P1

VSS_10

P9

VSS_11

T1

VSS_12

T9

VSSQ_1

B1

VSSQ_2

B9

VSSQ_3

D1

VSSQ_4

D8

VSSQ_5

E2

VSSQ_6

E8

VSSQ_7

F9

VSSQ_8

G1

VSSQ_9

G9

+3.5V_ST_WAKE

AVDD_33SB

C539

0.1uF

OPT

C541

0.1uF

16V

OPT

C509

0.1uF

C511

0.1uF

L502

BLM18PG121SN1D

OPT

C535

0.1uF

OPT

C531

0.1uF

16V

C507

0.1uF

L505

BLM18PG121SN1D

C514

10uF

C508

2.2uF

C504

0.1uF

C503

10uF

C520

0.1uF

L504

BLM18PG121SN1D

C506

0.1uF

C505

10uF

C523

1uF

C517

10uF

C532

0.1uF

C518

10uF

L501

BLM18PG121SN1D

C527

0.1uF

OPT

C513

10uF

OPT

L503

BLM18PG121SN1D

OPT

C747

0.1uF

TP700

C741

0.1uF

R730

1K

1%

C742

0.1uF

R727

1K

1%

C746

0.1uF

C700

0.1uF

R731

1K

1%

TP701

R726

1K

1%

C735

0.1uF

C736

0.1uF

C716

0.1uF

R721

1K

1%

C713

0.1uF

R718

1K

1%

C733

0.1uF

R709

1K

1%

C714

0.1uF

R710

240

1%

R708

1K

1%

R712

100

5%

R716

240

1%

R706

1K

1%

R719

1K

1%

R720

1K

1%

C734

0.1uF

C715

0.1uF

R714

100

5%

R707

1K

1%

C709

0.1uF

R713

100

5%

R705

1K

1%

R702

1K

1%

C712

0.1uF

R703

1K

1%

C710

0.1uF

C711

0.1uF

R711

240

1%

R704

1K

1%

H5TQ2G63BFR-PBC

IC702

DDR_256M_HYNIX

A0

N3

A1

P7

A2

P3

A3

N2

A4

P8

A5

P2

A6

R8

A7

R2

A8

T8

A9

R3

A10/AP

L7

A11

R7

A12/BC

N7

A13

T3

A15

M7

BA0

M2

BA1

N8

BA2

M3

CK

J7

CK

K7

CKE

K9

CS

L2

ODT

K1

RAS

J3

CAS

K3

WE

L3

RESET

T2

DQSL

F3

DQSL

G3

DQSU

C7

DQSU

B7

DML

E7

DMU

D3

DQL0

E3

DQL1

F7

DQL2

F2

DQL3

F8

DQL4

H3

DQL5

H8

DQL6

G2

DQL7

H7

DQU0

D7

DQU1

C3

DQU2

C8

DQU3

C2

DQU4

A7

DQU5

A2

DQU6

B8

DQU7

A3

VREFCA

M8

VREFDQ

H1

ZQ

L8

VDD_1

B2

VDD_2

D9

VDD_3

G7

VDD_4

K2

VDD_5

K8

VDD_6

N1

VDD_7

N9

VDD_8

R1

VDD_9

R9

VDDQ_1

A1

VDDQ_2

A8

VDDQ_3

C1

VDDQ_4

C9

VDDQ_5

D2

VDDQ_6

E9

VDDQ_7

F1

VDDQ_8

H2

VDDQ_9

H9

NC_1

J1

NC_2

J9

NC_3

L1

NC_4

L9

NC_6

T7

VSS_1

A9

VSS_2

B3

VSS_3

E1

VSS_4

G8

VSS_5

J2

VSS_6

J8

VSS_7

M1

VSS_8

M9

VSS_9

P1

VSS_10

P9

VSS_11

T1

VSS_12

T9

VSSQ_1

B1

VSSQ_2

B9

VSSQ_3

D1

VSSQ_4

D8

VSSQ_5

E2

VSSQ_6

E8

VSSQ_7

F9

VSSQ_8

G1

VSSQ_9

G9

C728

0.1uF

C701

10uF

10V

C725

0.1uF

1uF

C703

C717

0.1uF

C750

0.1uF

C727

0.1uF

C723

0.1uF

C726

0.1uF

C720

0.1uF

C718

0.1uF

1uF

C706

C708

10uF

10V

C719

0.1uF

C722

0.1uF

C751

0.1uF

C753

0.1uF

C704

10uF

10V

C754

0.1uF

1uF

C702

C745

0.1uF

C755

0.1uF

C707

10uF

10V

1uF

C705

R500

10K

Q500

MMBT3904(NXP)

E

B

C

Q501

PMV48XP

G

D

S

K4B4G1646B-HCK0

IC701

DDR_512M_SS

A0

N3

A1

P7

A2

P3

A3

N2

A4

P8

A5

P2

A6

R8

A7

R2

A8

T8

A9

R3

A10/AP

L7

A11

R7

A12/BC

N7

A13

T3

A15

M7

BA0

M2

BA1

N8

BA2

M3

CK

J7

CK

K7

CKE

K9

CS

L2

ODT

K1

RAS

J3

CAS

K3

WE

L3

RESET

T2

DQSL

F3

DQSL

G3

DQSU

C7

DQSU

B7

DML

E7

DMU

D3

DQL0

E3

DQL1

F7

DQL2

F2

DQL3

F8

DQL4

H3

DQL5

H8

DQL6

G2

DQL7

H7

DQU0

D7

DQU1

C3

DQU2

C8

DQU3

C2

DQU4

A7

DQU5

A2

DQU6

B8

DQU7

A3

VREFCA

M8

VREFDQ

H1

ZQ

L8

VDD_1

B2

VDD_2

D9

VDD_3

G7

VDD_4

K2

VDD_5

K8

VDD_6

N1

VDD_7

N9

VDD_8

R1

VDD_9

R9

VDDQ_1

A1

VDDQ_2

A8

VDDQ_3

C1

VDDQ_4

C9

VDDQ_5

D2

VDDQ_6

E9

VDDQ_7

F1

VDDQ_8

H2

VDDQ_9

H9

NC_1

J1

NC_2

J9

NC_3

L1

NC_4

L9

A14

T7

VSS_1

A9

VSS_2

B3

VSS_3

E1

VSS_4

G8

VSS_5

J2

VSS_6

J8

VSS_7

M1

VSS_8

M9

VSS_9

P1

VSS_10

P9

VSS_11

T1

VSS_12

T9

VSSQ_1

B1

VSSQ_2

B9

VSSQ_3

D1

VSSQ_4

D8

VSSQ_5

E2

VSSQ_6

E8

VSSQ_7

F9

VSSQ_8

G1

VSSQ_9

G9

K4B4G1646B-HCK0

IC703

DDR_512M_SS

A0

N3

A1

P7

A2

P3

A3

N2

A4

P8

A5

P2

A6

R8

A7

R2

A8

T8

A9

R3

A10/AP

L7

A11

R7

A12/BC

N7

A13

T3

A15

M7

BA0

M2

BA1

N8

BA2

M3

CK

J7

CK

K7

CKE

K9

CS

L2

ODT

K1

RAS

J3

CAS

K3

WE

L3

RESET

T2

DQSL

F3

DQSL

G3

DQSU

C7

DQSU

B7

DML

E7

DMU

D3

DQL0

E3

DQL1

F7

DQL2

F2

DQL3

F8

DQL4

H3

DQL5

H8

DQL6

G2

DQL7

H7

DQU0

D7

DQU1

C3

DQU2

C8

DQU3

C2

DQU4

A7

DQU5

A2

DQU6

B8

DQU7

A3

VREFCA

M8

VREFDQ

H1

ZQ

L8

VDD_1

B2

VDD_2

D9

VDD_3

G7

VDD_4

K2

VDD_5

K8

VDD_6

N1

VDD_7

N9

VDD_8

R1

VDD_9

R9

VDDQ_1

A1

VDDQ_2

A8

VDDQ_3

C1

VDDQ_4

C9

VDDQ_5

D2

VDDQ_6

E9

VDDQ_7

F1

VDDQ_8

H2

VDDQ_9

H9

NC_1

J1

NC_2

J9

NC_3

L1

NC_4

L9

A14

T7

VSS_1

A9

VSS_2

B3

VSS_3

E1

VSS_4

G8

VSS_5

J2

VSS_6

J8

VSS_7

M1

VSS_8

M9

VSS_9

P1

VSS_10

P9

VSS_11

T1

VSS_12

T9

VSSQ_1

B1

VSSQ_2

B9

VSSQ_3

D1

VSSQ_4

D8

VSSQ_5

E2

VSSQ_6

E8

VSSQ_7

F9

VSSQ_8

G1

VSSQ_9

G9

IC105

LGE2122[A2_M13]

VCCK_1

L11

VCCK_2

N12

VCCK_3

P12

VCCK_4

AG5

VCCK_5

AH5

VCCK_6

AJ5

VCCK_7

AK5

VCCK_8

AL5

VCCK_9

AM5

VCCK_10

AN5

VCCK_11

AK6

VCCK_12

AL6

VCCK_13

AM6

VCCK_14

AN6

VCCK_15

M11

VCCK_16

N11

VCCK_17

P11

VCCK_18

R11

VCCK_19

M12

VCCK_20

R12

VCCK_21

L13

VCCK_22

L14

VCCK_23

L15

VCCK_24

L17

VCCK_25

L18

VCCK_26

L19

VCCK_27

T11

VCCK_28

U11

VCCK_29

V11

VCCK_30

W11

VCCK_31

Y11

VCCK_32

AA11

VCCK_33

AB11

VCCK_34

AC11

VCCK_35

R23

VCCK_36

L12

VCCK_37

W12

VCCK_38

V23

VCCK_39

Y12

VCCK_40

AF6

VCCK_41

AG6

VCCK_42

AH6

VCCK_43

AJ6

VCCK_44

AE7

VCCK_45

AF7

VCCK_46

AG7

VCCK_47

AD8

VCCK_48

AE8

VCCK_49

AF8

VCCK_50

AE9

VCCK_51

AC10

VCCK_52

AD10

VCCK_53

AD11

VCCK_54

AE10

VCCK_55

AF9

VCCK_56

AG8

VCCK_57

AH7

VCCK_58

AJ7

VCCK_59

AK7

VCCK_60

AL7

VCCK_61

AM7

VCCK_62

AN7

VCCK_63

L16

VCCK_64

V12

VCCK_65

U12

VCCK_66

T12

VCCK_67

AD13

VCCK_68

AD17

VCCK_69

AD14

VCCK_70

AB12

VCCK_71

AA12

VCCK_72

AC12

VCC3IO_C

T9

VCC3IO_B_1

Y10

VCC3IO_B_2

AA10

VCC3IO_A_1

D22

VCC3IO_A_2

E22

DVSS_1

AC18

DVSS_2

AB21

DVSS_3

AB14

DVSS_4

N13

DVSS_5

P13

DVSS_6

R13

DVSS_7

T13

DVSS_8

U13

DVSS_9

V13

DVSS_10

W13

DVSS_11

Y13

DVSS_12

P18

DVSS_13

N14

DVSS_14

P14

DVSS_15

R14

DVSS_16

T14

DVSS_17

U14

DVSS_18

V14

DVSS_19

W14

DVSS_20

Y14

DVSS_21

R18

DVSS_22

N15

DVSS_23

P15

DVSS_24

R15

DVSS_25

T15

DVSS_26

U15

DVSS_27

V15

DVSS_28

W15

DVSS_29

Y15

DVSS_30

AA15

DVSS_31

AB15

DVSS_32

T18

DVSS_33

R16

DVSS_34

T16

DVSS_35

U16

DVSS_36

V16

DVSS_37

W16

DVSS_38

Y16

DVSS_39

AA16

DVSS_40

AB16

DVSS_41

R17

DVSS_42

T17

DVSS_43

U17

DVSS_44

V17

DVSS_45

Y17

DVSS_46

N16

DVSS_47

V18

DVSS_48

Y18

DVSS_49

P16

DVSS_50

V19

DVSS_51

Y19

DVSS_52

W17

DVSS_53

AA17

DVSS_54

AB17

DVSS_55

N19

DVSS_56

AC14

DVSS_57

C13

DVSS_58

K24

DVSS_59

K25

DVSS_60

L24

DVSS_61

M17

DVSS_62

M18

DVSS_63

M19

DVSS_64

P17

DVSS_65

P19

DVSS_66

N18

DVSS_67

U20

DVSS_68

V20

DVSS_69

W20

DVSS_70

Y20

DVSS_71

AA20

DVSS_72

R19

DVSS_73

T19

DVSS_74

M20

DVSS_75

N20

DVSS_76

U21

DVSS_77

V21

DVSS_78

W21

DVSS_79

Y21

DVSS_80

AA21

DVSS_81

P20

DVSS_82

R20

DVSS_83

T20

DVSS_84

U22

DVSS_85

V22

DVSS_86

W22

DVSS_87

Y22

DVSS_88

AA22

DVSS_89

N21

DVSS_90

P21

DVSS_91

R21

DVSS_92

T21

DVSS_93

M22

DVSS_94

N22

DVSS_95

P22

DVSS_96

R22

DVSS_97

T22

DVSS_98

M21

DVSS_99

AC17

DVSS_100

AA19

DVSS_101

M13

DVSS_102

M14

DVSS_103

M15

DVSS_104

AA13

DVSS_105

AB13

DVSS_106

AA14

DVSS_107

AB19

DVSS_108

D6

DVSS_109

W19

DVSS_110

U19

DVSS_111

N17

DVSS_112

L3

DVSS_113

AB18

DVSS_114

AA18

DVSS_115

W18

DVSS_116

U18

DVSS_117

D16

DVSS_118

AC13

DVSS_119

M16

DVSS_120

AC20

DVSS_121

AC22

DVSS_122

AD20

DVSS_123

Y23

DVSS_124

AA23

DVSS_125

AB23

DVSS_126

V24

DVSS_127

W23

IC105

LGE2122[A2_M13]

DDRV_1

R1

DDRV_2

R2

DDRV_3

R3

DDRV_4

R4

DDRV_5

R5

DDRV_6

K3

DDRV_7

R6

DDRV_8

L8

DDRV_9

M8

DDRV_10

D17

DDRV_11

A19

MEMTP

J22

MEMTN

K22

RVREF_A

D18

ARCKE

G8

ARCLK1

B5

ARCLK1

A5

ARCLK0

B14

ARCLK0

A14

ARODT

F13

ARRAS

E13

ARCAS

G13

ARCS

G15

ARWE

H18

ARRESET

G16

ARBA0

D15

ARBA1

F9

ARBA2

G18

ARCSX

F15

ARA14

D11

ARA13

F16

ARA12

D8

ARA11

E11

ARA10

G9

ARA9

E16

ARA8

F11

ARA

G17

ARA6

F10

ARA5

E17

ARA4

E10

ARA3

E15

ARA2

F17

ARA1

G10

ARA0

F18

ARDQM0

D12

ARDQS0

D14

ARDQS0

C14

ARDQ0

B17

ARDQ1

D10

ARDQ2

C17

ARDQ3

C10

ARDQ4

C18

ARDQ5

B9

ARDQ6

E18

ARDQ7

D9

ARDQM1

C15

ARDQS1

A13

ARDQS1

B13

ARDQ8

B11

ARDQ9

B16

ARDQ10

A11

ARDQ11

A17

ARDQ12

C12

ARDQ13

A16

ARDQ14

C11

ARDQ15

C16

ARDQM2

A3

ARDQS2

D5

ARDQS2

C5

ARDQ16

E7

ARDQ17

B2

ARDQ18

C8

ARDQ19

B1

ARDQ20

A9

ARDQ21

C1

ARDQ22

C9

ARDQ23

C3

ARDQM3

C6

ARDQS3

A4

ARDQS3

B4

ARDQ24

A1

ARDQ25

B7

ARDQ26

C4

ARDQ27

C7

ARDQ28

B3

ARDQ29

A7

ARDQ30

A2

ARDQ31

D7

AVDD33_MEMPLL

A20

AVSS33_MEMPLL

H9

IC105

LGE2122[A2_M13]

RVREF_C

C2

BRCLK0

J2

BRCLK0

J1

BRCKE

L6

BRODT

E3

BRRAS

L4

BRCAS

D3

BRCS

D4

BRBA0

J4

BRBA1

M6

BRBA2

E4

BRWE

K4

BRA15

J3

BRA14

P4

BRA13

G5

BRA12

P6

BRA11

P5

BRA10

L5

BRA9

F4

BRA8

P3

BRA7

H4

BRA6

P2

BRA5

K6

BRA4

M5

BRA3

K5

BRA2

G6

BRA1

N5

BRA0

E5

DDRV_12

B19

DDRV_13

C19

DDRV_14

D19

DDRV_15

E19

DDRV_16

F19

DDRV_17

G19

DDRV_18

F5

DDRV_19

H5

DDRV_20

N8

DDRV_21

P8

DDRV_22

D13

DDRV_23

E8

DDRV_24

G11

DDRV_25

D20

DDRV_26

E20

DDRV_27

F20

DDRV_28

G20

DDRV_29

R7

DDRV_30

R8

DDRV_31

T5

DDRV_32

T6

DDRV_33

T7

DDRV_34

T8

BRDQM0

L1

BRDQS0

H2

BRDQS0

H1

BRDQ0

E2

BRDQ1

N3

BRDQ2

E1

BRDQ3

N1

BRDQ4

D1

BRDQ5

P1

BRDQ6

D2

BRDQ7

N2

BRDQM1

H3

BRDQS1

K1

BRDQS1

K2

BRDQ8

N4

BRDQ9

F2

BRDQ10

M3

BRDQ11

F1

BRDQ12

L2

BRDQ13

F3

BRDQ14

M4

BRDQ15

G3

BRRESET

G4

ZD500

5V

OPT

C500

4.7uF

10V

OPT

R502

10K

C501

4.7uF

10V

C502

0.1uF

16V

OPT

R501

1.8K

IC500

AP2121N-3.3TRE1

1

GND

2

VOUT

3

VIN

C512

1uF

10V

C510

0.1uF

16V

TP503

TP502

DECAP FOR SOC Rework (BOTTOM)DECAP FOR SOC (HIDDEN - UCC)

60mA

5600mA

20120813 LCD-TV

29LN460

2012.12.22

2 8MAIN/DDR

20120813 SI.HAN

20120813 CJ.LIM

LCD-TV

DECAP_HIDDEN_1.5V -> APPLY

2012.10.16 LCD-TV

2012.10.16 LCD-TV

EAX65323501

[MP]

Copyright © 2013 LG Electronics. Inc. All rights reserved.

Only for training and service purposes

LGE Internal Use Only