THE SYMBOL MARK OF THIS SCHEMETIC DIAGRAM INCORPORATES

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

SIGN50000

SIGN50005

M2_DDR_BA1

R738

240

M2_DDR_A3

M2_DDR_RESET_N

M2_DDR_VREFCA

M2_DDR_A10

M2_DDR_DQSL_N

M2_DDR_DQ6

M2_DDR_DMU

M2_DDR_DQ13

M2_DDR_A0

C744

10uF

10V

C739

0.1uF

M2_DDR_DQ8

M2_DDR_A6

M2_DDR_DQ7

C741

0.1uF

M2_DDR_DML

M2_DDR_A9

M2_DDR_DQSL_P

C742

0.1uF

M2_DDR_RASN

M2_DDR_DQ14

M2_DDR_A8

M2_DDR_DQ5

M2_DDR_ODT

M2_DDR_DQ2

C736

0.1uF

M2_DDR_DQ15

C740

0.1uF

M2_DDR_DQ0

M2_DDR_DQ1

M2_DDR_DQ10

M2_DDR_WEN

M2_DDR_A11

C738

0.1uF

M2_DDR_A4

M2_DDR_CASN

M2_DDR_DQ11

M2_DDR_A1

M2_DDR_DQ12

M2_DDR_A5

M2_DDR_DQ3

M2_DDR_A12

M2_DDR_CKE

M2_DDR_BA0

M2_DDR_DQ9

M2_DDR_DQSU_N

VCC1.5V_DE

M2_DDR_DQSU_P

M2_DDR_VREFDQ

M2_DDR_A13

C737

0.1uF

M2_DDR_A7

M2_DDR_BA2

M2_DDR_A2

C743

0.1uF

M2_DDR_DQ4

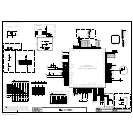

H5TQ1G63DFR-PBC

IC702

A0

N3

A1

P7

A2

P3

A3

N2

A4

P8

A5

P2

A6

R8

A7

R2

A8

T8

A9

R3

A10/AP

L7

A11

R7

A12/BC

N7

A13

T3

A15

M7

BA0

M2

BA1

N8

BA2

M3

CK

J7

CK

K7

CKE

K9

CS

L2

ODT

K1

RAS

J3

CAS

K3

WE

L3

RESET

T2

DQSL

F3

DQSL

G3

DQSU

C7

DQSU

B7

DML

E7

DMU

D3

DQL0

E3

DQL1

F7

DQL2

F2

DQL3

F8

DQL4

H3

DQL5

H8

DQL6

G2

DQL7

H7

DQU0

D7

DQU1

C3

DQU2

C8

DQU3

C2

DQU4

A7

DQU5

A2

DQU6

B8

DQU7

A3

VREFCA

M8

VREFDQ

H1

ZQ

L8

VDD_1

B2

VDD_2

D9

VDD_3

G7

VDD_4

K2

VDD_5

K8

VDD_6

N1

VDD_7

N9

VDD_8

R1

VDD_9

R9

VDDQ_1

A1

VDDQ_2

A8

VDDQ_3

C1

VDDQ_4

C9

VDDQ_5

D2

VDDQ_6

E9

VDDQ_7

F1

VDDQ_8

H2

VDDQ_9

H9

NC_1

J1

NC_2

J9

NC_3

L1

NC_4

L9

NC_6

T7

VSS_1

A9

VSS_2

B3

VSS_3

E1

VSS_4

G8

VSS_5

J2

VSS_6

J8

VSS_7

M1

VSS_8

M9

VSS_9

P1

VSS_10

P9

VSS_11

T1

VSS_12

T9

VSSQ_1

B1

VSSQ_2

B9

VSSQ_3

D1

VSSQ_4

D8

VSSQ_5

E2

VSSQ_6

E8

VSSQ_7

F9

VSSQ_8

G1

VSSQ_9

G9

C722

0.1uF

C721

0.1uF

C705

0.1uF

C704

0.1uF

C720

0.1uF

VCC1.5V_MAIN

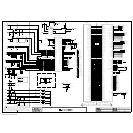

M0_DDR_VREFCA

M0_DDR_VREFDQ

VCC1.5V_MAIN

M0_1_DDR_VREFCA

M0_DDR_A5

R735

1K 1%

C751

0.1uF

C708

0.1uF

M1_DDR_DQSL_N

M0_DDR_BA0

VCC1.5V_MAIN

M0_DDR_RESET_N

M1_DDR_CKE

M0_DDR_RASN

M0_DDR_CLK

M1_DDR_DQSU_P

C707

0.1uF

M1_DDR_DQ1

R736

1K1%

M1_DDR_DQ5

C735

0.1uF

M0_DDR_CLK

C733

0.1uF

R721

240

1%

C758

0.1uF

M1_DDR_A6

M0_DDR_A1

C715

0.1uF

M0_DDR_DQ3

C761

0.1uF

M1_DDR_A10

M1_DDR_A14

M0_DDR_A8

M1_DDR_A3

M1_DDR_BA0

C728

1000pF

VCC1.5V_MAIN

M1_DDR_DQ3

M0_DDR_DQSL_N

R730

1K1%

M1_1_DDR_VREFDQ

C723

0.1uF

M1_DDR_A5

C729

1000pF

M0_1_DDR_VREFCA

M0_DDR_DMU

M0_DDR_CLKN

M0_DDR_ODT

M0_DDR_CLKN

M1_DDR_DQ10

M1_DDR_DQ2

M1_DDR_BA2

C752

0.1uF

M0_DDR_A9

C711

0.1uF

M1_DDR_DQSU_N

M0_DDR_A0

M1_DDR_RESET_N

M0_DDR_A11

M1_DDR_CLK

M1_DDR_VREFDQ

M0_DDR_BA1

M0_DDR_DQ12

M1_DDR_CASN

M1_DDR_A3

M0_DDR_DQ9

M1_DDR_A9

M0_DDR_DQ15

M0_DDR_A12

R727

1K 1%

M1_DDR_DQ4

M0_DDR_BA1

M1_DDR_A5

M0_DDR_A7

C748

1000pF

M0_DDR_CASN

C710

0.1uF

M1_DDR_DQ14

M1_DDR_A13

VCC1.5V_MAIN

M1_DDR_BA0

VCC1.5V_MAIN

M1_DDR_RESET_N

VCC1.5V_MAIN

M1_DDR_CKE

C732

0.1uF

VCC1.5V_MAIN

C724

0.1uF

M0_DDR_DQ6

M1_DDR_A12

M0_DDR_A10

R729

1K 1%

C745

0.1uF

R741

10K

C716

0.1uF

M0_1_DDR_VREFDQ

M1_DDR_DQ11

R737

1K 1%

C753

0.1uF

M1_DDR_A4

M0_DDR_RESET_N

M1_DDR_DML

M0_DDR_A11

R740

240

1%

M0_DDR_A4

M1_DDR_CASN

M0_DDR_CLK

M0_DDR_BA0

C717

0.1uF

M0_DDR_CLK

M1_DDR_DQ8

C709

0.1uF

R742

10K

M1_DDR_BA1

M1_DDR_CLK

R720

240

1%

C747

1000pF

M0_DDR_VREFDQ

M1_DDR_RESET_N

C749

1000pF

M0_DDR_BA2

M0_DDR_A10

M1_1_DDR_VREFCA

M1_DDR_DQ13

C757

0.1uF

R709

10K

R739

240

1%

M0_DDR_A13

M1_DDR_A2

M1_DDR_WEN

M0_DDR_DQSL_P

M1_DDR_BA2

M1_DDR_A7

M1_DDR_A0

M1_DDR_A6

M0_DDR_RASN

M0_DDR_WEN

M1_DDR_CKE

M1_DDR_A11

M1_DDR_DQ9

M0_DDR_DQ11M0_DDR_DQ7

M0_DDR_DQ10

M1_DDR_BA1

M1_DDR_DMU

M0_DDR_A14

VCC1.5V_MAIN

M1_DDR_A1

M0_DDR_CLKN

M0_DDR_A6

M1_DDR_CLKN

M1_DDR_DQ7

C731

1000pF

C719

0.1uF

M0_DDR_WEN

M0_DDR_ODT

M1_DDR_DQ0

C750

1000pF

C746

0.1uF

M1_DDR_DQ6

C730

1000pF

C718

0.1uF

C726

0.1uF

M0_DDR_A0

R734

1K1%

R723

1K 1%

C706 0.1uF

M0_DDR_DQSU_P

M1_DDR_DQ12

M1_DDR_WEN

M0_DDR_A3

M1_DDR_ODT

M1_DDR_A2

R726

1K1%

M0_DDR_DQ14

M0_DDR_A7

VCC1.5V_MAIN

R733

1K 1%

M0_DDR_A6

C727

0.1uF

M0_DDR_BA2

M0_DDR_VREFCA

M0_1_DDR_VREFDQ

VCC1.5V_MAIN

R710

10K

M1_DDR_CLKN

C759

0.1uF

C734

0.1uF

M1_1_DDR_VREFCA

M1_DDR_A1

M1_DDR_DQSL_P

M1_DDR_RASN

M1_DDR_A13

M0_DDR_DQSU_N

M0_DDR_DQ0

M0_DDR_RESET_N

R731

1K 1%

M0_DDR_A14

M1_DDR_CLK

M1_DDR_CLKN

M1_DDR_A7

M1_DDR_A4

VCC1.5V_MAIN

M0_DDR_CASN

M0_DDR_A3

M1_DDR_A12

C714

0.1uF

M1_DDR_CLK

R732

1K1%

R725

1K 1%

C713

0.1uF

M0_DDR_A8

M1_DDR_VREFCA

M0_DDR_DQ1

M1_DDR_A11

M1_1_DDR_VREFDQ

C725

0.1uF

M0_DDR_DQ8

M1_DDR_RASN

VCC1.5V_MAIN

M0_DDR_A4

M0_DDR_CKE

R722

1K1%

M0_DDR_CKE

M1_DDR_A0

M1_DDR_A8

C760

0.1uF

M0_DDR_A5

M1_DDR_A10

C754

0.1uF

M0_DDR_A1

M1_DDR_VREFCA

M1_DDR_ODT

M1_DDR_A14

M0_DDR_CLKN

M0_DDR_A12

M0_DDR_DQ5

C712

0.1uF

VCC1.5V_MAIN

M1_DDR_A9

M1_DDR_VREFDQ

M0_DDR_A2

C755

0.1uF

R724

1K1%

M0_DDR_A9

M1_DDR_A8

M1_DDR_CLKN

M0_DDR_DQ13

M0_DDR_A2

C756

0.1uF

R728

1K1%

M0_DDR_A13

M0_DDR_DQ2

M0_DDR_DML

M0_DDR_CKE

M0_DDR_DQ4

M1_DDR_DQ15

M0_DDR_BA1

M1_DDR_A8

M1_DDR_DQ4

M1_DDR_DQSL_P

M1_DDR_A2

M1_DDR_A4

M0_DDR_DQ11

M0_DDR_DQ0

M1_DDR_DQ15

M1_DDR_DQ10

M1_DDR_DQSL_N

M0_DDR_DQ12

M0_DDR_A14

M0_DDR_A9

M1_DDR_BA0

M0_DDR_WEN

M0_DDR_RESET_N

M0_DDR_BA0

M0_DDR_DQ14

M0_DDR_CKE

M1_DDR_DQSU_P

M0_DDR_A1

M0_DDR_DQSU_N

M0_DDR_DQSL_P

M0_DDR_DML

M0_DDR_A6

M0_DDR_A7

M0_DDR_ODT

M1_DDR_A6

M1_DDR_WEN

M1_DDR_DQ6

M0_DDR_A2

M0_DDR_DQ2

M1_DDR_DQ8

M0_DDR_A5

M1_DDR_A10

M0_DDR_CLK

M1_DDR_DQ0

M0_DDR_DQ5

M1_DDR_A1

M1_DDR_A7

M1_DDR_A13

M0_DDR_A0

M0_DDR_A4

M1_DDR_DQ7

M1_DDR_CLKN

M0_DDR_DQ8

M1_DDR_ODT

M0_DDR_A12

M0_DDR_DQ9

M0_DDR_A3

M1_DDR_RESET_N

M0_DDR_DQ13

M1_DDR_A11

M1_DDR_RASN

M1_DDR_DQ13

M1_DDR_DQ9

M0_DDR_DQ7

M0_DDR_A13

M1_DDR_CASN

M1_DDR_A5

M0_DDR_A8

M1_DDR_DML

M1_DDR_BA1

M0_DDR_DQ1

R704

240

1%

M0_DDR_BA2

M0_DDR_RASN

M1_DDR_A0

M1_DDR_DQ1

M0_DDR_CASN

M0_DDR_A11

M1_DDR_DQ14

M1_DDR_DQ3

M1_DDR_A12

M1_DDR_DQ2

M0_DDR_DMU

M1_DDR_DQ5

M0_DDR_DQ6

M0_DDR_DQ3

M1_DDR_DQSU_N

M1_DDR_DQ11

M1_DDR_DQ12

M0_DDR_CLKN

M0_DDR_DQ10

M1_DDR_BA2

M1_DDR_CLK

M1_DDR_A3

M0_DDR_DQ15

M1_DDR_DMU

M1_DDR_A9

M1_DDR_A14

M0_DDR_DQ4

M0_DDR_DQSL_N

M1_DDR_CKE

M0_DDR_A10

M0_DDR_DQSU_P

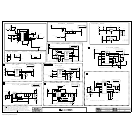

M2_DDR_WEN

M2_DDR_A3

M2_DDR_DQ5

M2_DDR_A2

M2_DDR_DQ1

M2_DDR_CKE

M2_DDR_A12

M2_DDR_DQ6

M2_DDR_A1

M2_DDR_DQ7

M2_DDR_A11

M2_DDR_DQ11

M2_DDR_DQ3

M2_DDR_DQ4

M2_DDR_DQ9

M2_DDR_A13

M2_DDR_DQ14

M2_DDR_BA0

M2_DDR_CLK

M2_DDR_CLKN

M2_DDR_RASN

M2_DDR_DQSU_P

M2_DDR_BA1

M2_DDR_DML

M2_DDR_RESET_N

M2_DDR_DMU

M2_DDR_DQ13

M2_DDR_A5

M2_DDR_A9

M2_DDR_DQ2

M2_DDR_DQ10

M2_DDR_A10

M2_DDR_DQSL_P

M2_DDR_DQSL_N

M2_DDR_DQ8

M2_DDR_DQSU_N

M2_DDR_ODT

M2_DDR_DQ0

M2_DDR_DQ12

M2_DDR_A0

M2_DDR_A6

M2_DDR_CASN

M2_DDR_DQ15

R711

240

1%

M2_DDR_A8

M2_DDR_A7

M2_DDR_BA2

M2_DDR_A4

VCC1.5V_DE

R719

1K 1%

R712

1K1%

R718

1K1%

R743

10K

M2_DDR_VREFDQ

M2_DDR_CKE

C703

1000pF

M2_DDR_CLKN

M2_CLK

C700

0.1uF

R713

1K 1%

M2_CLKN

C701

1000pF

R714

10K

M2_DDR_CLK

M2_CLKN

M2_CLK

VCC1.5V_DE

C702

0.1uF

VCC1.5V_DE

M2_DDR_VREFCA

M2_DDR_RESET_N M2_CLK

M2_CLKN

H5TQ2G83BFR-PBC

IC700

NC_S1

A1

VSS_1

A2

VDD_1

A3

NC_1

A4

NF/TDQS

A8

VSS_2

A9

VDD_2

A10

NC_S2

A11

VSS_3

B2

VSSQ_1

B3

DQ0

B4

DM/TDQS

B8

VSSQ_2

B9

VDDQ_1

B10

VDDQ_2

C2

DQ2

C3

DQS

C4

DQ1

C8

DQ3

C9

VSSQ_3

C10

VSSQ_4

D2

DQ6

D3

DQS

D4

VDD_3

D8

VSS_4

D9

VSSQ_5

D10

VREFDQ

E2

VDDQ_3

E3

DQ4

E4

DQ7

E8

DQ5

E9

VDDQ_4

E10

NC_2

F2

VSS_5

F3

RAS

F4

CK

F8

VSS_6

F9

NC_3

F10

ODT

G2

VDD_4

G3

CAS

G4

CK

G8

VDD_5

G9

CKE

G10

NC_4

H2

CS

H3

WE

H4

A10/AP

H8

ZQ

H9

NC_5

H10

VSS_7

J2

BA0

J3

BA2

J4

NC_6

J8

VREFCA

J9

VSS_8

J10

VDD_6

K2

A3

K3

A0

K4

A12/BC

K8

BA1

K9

VDD_7

K10

VSS_9

L2

A5

L3

A2

L4

A1

L8

A4

L9

VSS_10

L10

VDD_8

M2

A7

M3

A9

M4

A11

M8

A6

M9

VDD_9

M10

NC_S3

N1

VSS_11

N2

RESET

N3

A13

N4

A14

N8

A8

N9

VSS_12

N10

NC_S4

N11

H5TQ2G83BFR-PBC

IC703

NC_S1

A1

VSS_1

A2

VDD_1

A3

NC_1

A4

NF/TDQS

A8

VSS_2

A9

VDD_2

A10

NC_S2

A11

VSS_3

B2

VSSQ_1

B3

DQ0

B4

DM/TDQS

B8

VSSQ_2

B9

VDDQ_1

B10

VDDQ_2

C2

DQ2

C3

DQS

C4

DQ1

C8

DQ3

C9

VSSQ_3

C10

VSSQ_4

D2

DQ6

D3

DQS

D4

VDD_3

D8

VSS_4

D9

VSSQ_5

D10

VREFDQ

E2

VDDQ_3

E3

DQ4

E4

DQ7

E8

DQ5

E9

VDDQ_4

E10

NC_2

F2

VSS_5

F3

RAS

F4

CK

F8

VSS_6

F9

NC_3

F10

ODT

G2

VDD_4

G3

CAS

G4

CK

G8

VDD_5

G9

CKE

G10

NC_4

H2

CS

H3

WE

H4

A10/AP

H8

ZQ

H9

NC_5

H10

VSS_7

J2

BA0

J3

BA2

J4

NC_6

J8

VREFCA

J9

VSS_8

J10

VDD_6

K2

A3

K3

A0

K4

A12/BC

K8

BA1

K9

VDD_7

K10

VSS_9

L2

A5

L3

A2

L4

A1

L8

A4

L9

VSS_10

L10

VDD_8

M2

A7

M3

A9

M4

A11

M8

A6

M9

VDD_9

M10

NC_S3

N1

VSS_11

N2

RESET

N3

A13

N4

A14

N8

A8

N9

VSS_12

N10

NC_S4

N11

H5TQ2G83BFR-PBC

IC704

NC_S1

A1

VSS_1

A2

VDD_1

A3

NC_1

A4

NF/TDQS

A8

VSS_2

A9

VDD_2

A10

NC_S2

A11

VSS_3

B2

VSSQ_1

B3

DQ0

B4

DM/TDQS

B8

VSSQ_2

B9

VDDQ_1

B10

VDDQ_2

C2

DQ2

C3

DQS

C4

DQ1

C8

DQ3

C9

VSSQ_3

C10

VSSQ_4

D2

DQ6

D3

DQS

D4

VDD_3

D8

VSS_4

D9

VSSQ_5

D10

VREFDQ

E2

VDDQ_3

E3

DQ4

E4

DQ7

E8

DQ5

E9

VDDQ_4

E10

NC_2

F2

VSS_5

F3

RAS

F4

CK

F8

VSS_6

F9

NC_3

F10

ODT

G2

VDD_4

G3

CAS

G4

CK

G8

VDD_5

G9

CKE

G10

NC_4

H2

CS

H3

WE

H4

A10/AP

H8

ZQ

H9

NC_5

H10

VSS_7

J2

BA0

J3

BA2

J4

NC_6

J8

VREFCA

J9

VSS_8

J10

VDD_6

K2

A3

K3

A0

K4

A12/BC

K8

BA1

K9

VDD_7

K10

VSS_9

L2

A5

L3

A2

L4

A1

L8

A4

L9

VSS_10

L10

VDD_8

M2

A7

M3

A9

M4

A11

M8

A6

M9

VDD_9

M10

NC_S3

N1

VSS_11

N2

RESET

N3

A13

N4

A14

N8

A8

N9

VSS_12

N10

NC_S4

N11

H5TQ2G83BFR-PBC

IC701

NC_S1

A1

VSS_1

A2

VDD_1

A3

NC_1

A4

NF/TDQS

A8

VSS_2

A9

VDD_2

A10

NC_S2

A11

VSS_3

B2

VSSQ_1

B3

DQ0

B4

DM/TDQS

B8

VSSQ_2

B9

VDDQ_1

B10

VDDQ_2

C2

DQ2

C3

DQS

C4

DQ1

C8

DQ3

C9

VSSQ_3

C10

VSSQ_4

D2

DQ6

D3

DQS

D4

VDD_3

D8

VSS_4

D9

VSSQ_5

D10

VREFDQ

E2

VDDQ_3

E3

DQ4

E4

DQ7

E8

DQ5

E9

VDDQ_4

E10

NC_2

F2

VSS_5

F3

RAS

F4

CK

F8

VSS_6

F9

NC_3

F10

ODT

G2

VDD_4

G3

CAS

G4

CK

G8

VDD_5

G9

CKE

G10

NC_4

H2

CS

H3

WE

H4

A10/AP

H8

ZQ

H9

NC_5

H10

VSS_7

J2

BA0

J3

BA2

J4

NC_6

J8

VREFCA

J9

VSS_8

J10

VDD_6

K2

A3

K3

A0

K4

A12/BC

K8

BA1

K9

VDD_7

K10

VSS_9

L2

A5

L3

A2

L4

A1

L8

A4

L9

VSS_10

L10

VDD_8

M2

A7

M3

A9

M4

A11

M8

A6

M9

VDD_9

M10

NC_S3

N1

VSS_11

N2

RESET

N3

A13

N4

A14

N8

A8

N9

VSS_12

N10

NC_S4

N11

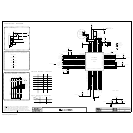

IC100

LG1152D-B1

M0_DDR_A0

D18

M0_DDR_A1

E17

M0_DDR_A2

E18

M0_DDR_A3

E20

M0_DDR_A4

E16

M0_DDR_A5

D20

M0_DDR_A6

F16

M0_DDR_A7

F19

M0_DDR_A8

E15

M0_DDR_A9

D19

M0_DDR_A10

D14

M0_DDR_A11

E14

M0_DDR_A12

D17

M0_DDR_A13

F18

M0_DDR_A14

D16

M0_DDR_BA0

F20

M0_DDR_BA1

D15

M0_DDR_BA2

F17

M0_DDR_CLK

A17

M0_DDR_CLKN

A18

M0_DDR_CKE

F15

M0_DDR_ODT

F21

M0_DDR_RASN

D22

M0_DDR_CASN

E21

M0_DDR_WEN

D21

M0_DDR_RESET_N

E19

M0_DDR_DQSL_P

B20

M0_DDR_DQSL_N

A20

M0_DDR_DQSU_P

B16

M0_DDR_DQSU_N

C16

M0_DDR_DML

C19

M0_DDR_DMU

C15

M0_DDR_DQ0

C20

M0_DDR_DQ1

B19

M0_DDR_DQ2

C21

M0_DDR_DQ3

B18

M0_DDR_DQ4

A21

M0_DDR_DQ5

C18

M0_DDR_DQ6

B21

M0_DDR_DQ7

A19

M0_DDR_DQ8

B17

M0_DDR_DQ9

C14

M0_DDR_DQ10

A16

M0_DDR_DQ11

B14

M0_DDR_DQ12

B15

M0_DDR_DQ13

A14

M0_DDR_DQ14

C17

M0_DDR_DQ15

A15

M0_DDR_ZQCAL

E22

IC100

LG1152D-B1

M1_DDR_A0

C9

M1_DDR_A1

E9

M1_DDR_A2

F10

M1_DDR_A3

F12

M1_DDR_A4

F8

M1_DDR_A5

D11

M1_DDR_A6

E8

M1_DDR_A7

E11

M1_DDR_A8

E7

M1_DDR_A9

D10

M1_DDR_A10

C4

M1_DDR_A11

C5

M1_DDR_A12

D8

M1_DDR_A13

E10

M1_DDR_A14

C7

M1_DDR_BA0

E12

M1_DDR_BA1

F7

M1_DDR_BA2

D9

M1_DDR_CLK

A9

M1_DDR_CLKN

B9

M1_DDR_CKE

D7

M1_DDR_ODT

D13

M1_DDR_RASN

C13

M1_DDR_CASN

E13

M1_DDR_WEN

D12

M1_DDR_RESET_N

F11

M1_DDR_DQSL_P

C12

M1_DDR_DQSL_N

C11

M1_DDR_DQSU_P

A7

M1_DDR_DQSU_N

B7

M1_DDR_DML

A11

M1_DDR_DMU

C6

M1_DDR_DQ0

A12

M1_DDR_DQ1

B11

M1_DDR_DQ2

A13

M1_DDR_DQ3

C10

M1_DDR_DQ4

B12

M1_DDR_DQ5

A10

M1_DDR_DQ6

B13

M1_DDR_DQ7

B10

M1_DDR_DQ8

A8

M1_DDR_DQ9

B4

M1_DDR_DQ10

C8

M1_DDR_DQ11

B5

M1_DDR_DQ12

B6

M1_DDR_DQ13

A5

M1_DDR_DQ14

B8

M1_DDR_DQ15

A6

IC100

LG1152D-B1

M2_DDR_A0

D1

M2_DDR_A1

K4

M2_DDR_A2

D2

M2_DDR_A3

E5

M2_DDR_A4

H6

M2_DDR_A5

E4

M2_DDR_A6

J4

M2_DDR_A7

D6

M2_DDR_A8

J5

M2_DDR_A9

D3

M2_DDR_A10

H4

M2_DDR_A11

J6

M2_DDR_A12

K5

M2_DDR_A13

D4

M2_DDR_BA0

E6

M2_DDR_BA1

H5

M2_DDR_BA2

F4

M2_DDR_CLK

M2

M2_DDR_CLKN

M3

M2_DDR_CKE

G6

M2_DDR_ODT

F6

M2_DDR_RASN

G5

M2_DDR_CASN

G4

M2_DDR_WEN

F5

M2_DDR_RESET_N

D5

M2_DDR_DQSU_P

H3

M2_DDR_DQSU_N

J1

M2_DDR_DQSL_P

H1

M2_DDR_DQSL_N

H2

M2_DDR_DML

K3

M2_DDR_DMU

F2

M2_DDR_DQ0

F1

M2_DDR_DQ1

L1

M2_DDR_DQ2

E3

M2_DDR_DQ3

L2

M2_DDR_DQ4

E1

M2_DDR_DQ5

M1

M2_DDR_DQ6

E2

M2_DDR_DQ7

L3

M2_DDR_DQ8

J3

M2_DDR_DQ9

G1

M2_DDR_DQ10

K2

M2_DDR_DQ11

F3

M2_DDR_DQ12

J2

M2_DDR_DQ13

G2

M2_DDR_DQ14

K1

M2_DDR_DQ15

G3

M2_DDR_ZQCAL

K6

R700 0

R701 0

R703 0

R702 0

R716 0

R717 0

R715

150

R705

200

R706

200

R708

200

R707

200

4MAIN DDR 50

LG1152 B0

DDR3 1.5V bypass Cap - Place these caps near Memory

DDR3

2Gbit

DDR3

2Gbit

DDR3

2Gbit

DDR3

2Gbit

Copyright © 2012 LG Electronics. Inc. All rights reserved.

Only for training and service purposes

LGE Internal Use Only