68

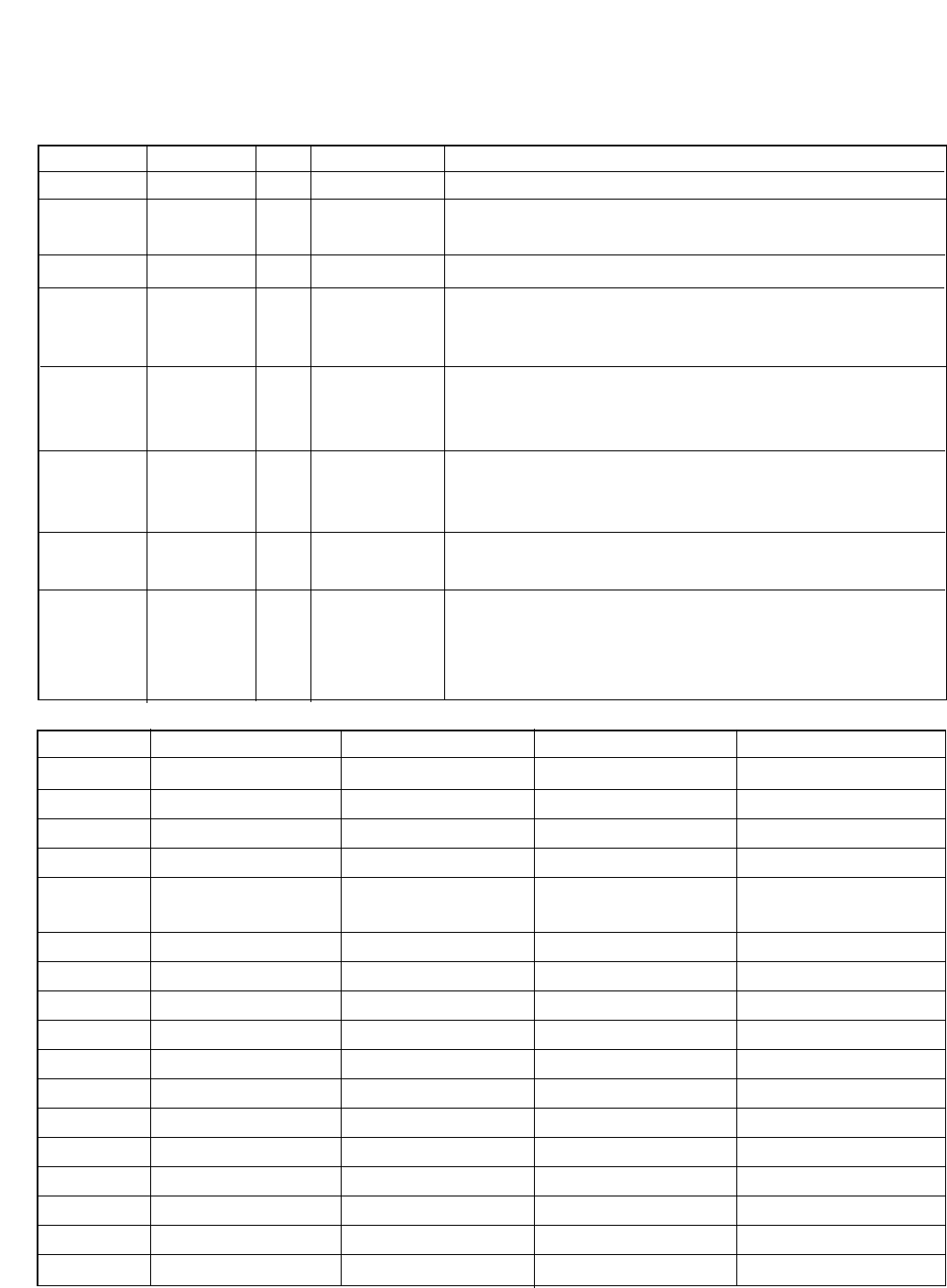

LSI/TEST Control Pin List

Pin Name Pin No. I/O destination Function

MRSTB 202 I RESET IC Master reset input

TESTB2 203 I Test select

TESTB1 204

TMS 114 IU E10emulator Test data switch for E10emulator

TCK 115 IOU E10emulator Test clock for E10 emulator

It can function as a SCI serial clock output port when E10

emulator is not used (multiplexed).

TDI 116 IU E10emulator Test data input for E10 emulator

It can function as a SCI serial data input port when E10

emulator is not used (multiplexed).

TDO 117 O E10emulator Test data output for E10 emulator

It can function as a SCI serial data output port when E10

emulator is not used (multiplexed).

TRST 118 I E10emulator Test reset for E10 emulator

/Non-mask CPU interrupt port(falling edge sense)

TEST0 110 IO User test/CPU general port2

TEST1 111 Test monitor can be set as the following table by a register

TEST2 112

TEST3 113

T*SEL[3:0] TEST0 TEST1 TEST2 TEST3

0 Servo monitor 0 Servo monitor 1 Servo monitor 2 Servo monitor 3

1 WPLL monitor 0 WPLL monitor 1 WPLL monitor 2 WPLL monitor 3

2 Audio 0 Audio 1 Audio 2 Audio 3

3 DVD modulation 0 DVD modulation 1 DVD modulation 2 DVD modulation 0

4 DVD-R/CD-R DVD-R/CD-R DVD-R/CD-R DVD-R/CD-R

monitor 0 monitor1 monitor 2 monitor 3

5 DVD+RW monitor 0 DVD+RW monitor1 DVD+RW monitor 2 DVD+RW monitor 3

6 PI/C1 PI/C1 PI/C1 PI/C1

7 PO/C2 PO/C2 PO/C2 PO/C2

8 DEMO 0 DEMO 1 DEMO 2 DEMO 3

9- - - -

10 CLVCK CLVCK CLVCK CLVCK

11 BLEND BLEND BLEND BLEND

12 PRML monitor 0 PRML monitor 1 PRML monitor 2 PRML monitor 3

13 Data PLL monitor 0 Data PLL monitor 1 Data PLL monitor 2 Data PLL monitor 3

14 RAMCON monitor 0 RAMCON monitor 1 RAMCOM monitor 2 RAMCON monitor 3

15 MIF monitor 0 MIF monitor 1 MIF monitor 2 MIF monitor 3

16 WOBREF monitor 0 WOBREF monitor 1 WOBREF monitor 2 WOBREF monitor 3

T*SEL can be set for each of pins TEST3, TEST2, TEST1, and TEST0, respectively.