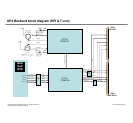

GP4 Backend block diagram (LVDS Tx & Local Dimming)

LVDS Tx

Block

Main SoC

MTK

LVDS_SEL

BIT_SEL_LOW

51Pin

LVDS

Output

PANEL_VCC

(+12V)

41Pin

LVDS

Output

10-bit (R)

Dual-link LVDS Output

24

10-bit (R)

24

Dual-link LVDS Output

• LVDS_SEL : “H”=JEIDA, “L” or NC=VESA (LGD)

• BIT_SEL : “H” or NC = 10-bit, “L” = 8-bit

L/DIMO_SCLK

L/DIMO_MOSI

I2C_SCL1

I2C_SDA1

L/DIMO_VS

[LDM_CK]

[LDM_VSYNC]

[STB_SCL]

[LDM_D0]

[STB_SDA]

Copyright © 2012 LG Electronics. Inc. All rights reserved.

Only for training and service purposes

LGE Internal Use Only