THE SYMBOL MARK OF THIS SCHEMETIC DIAGRAM INCORPORATES

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

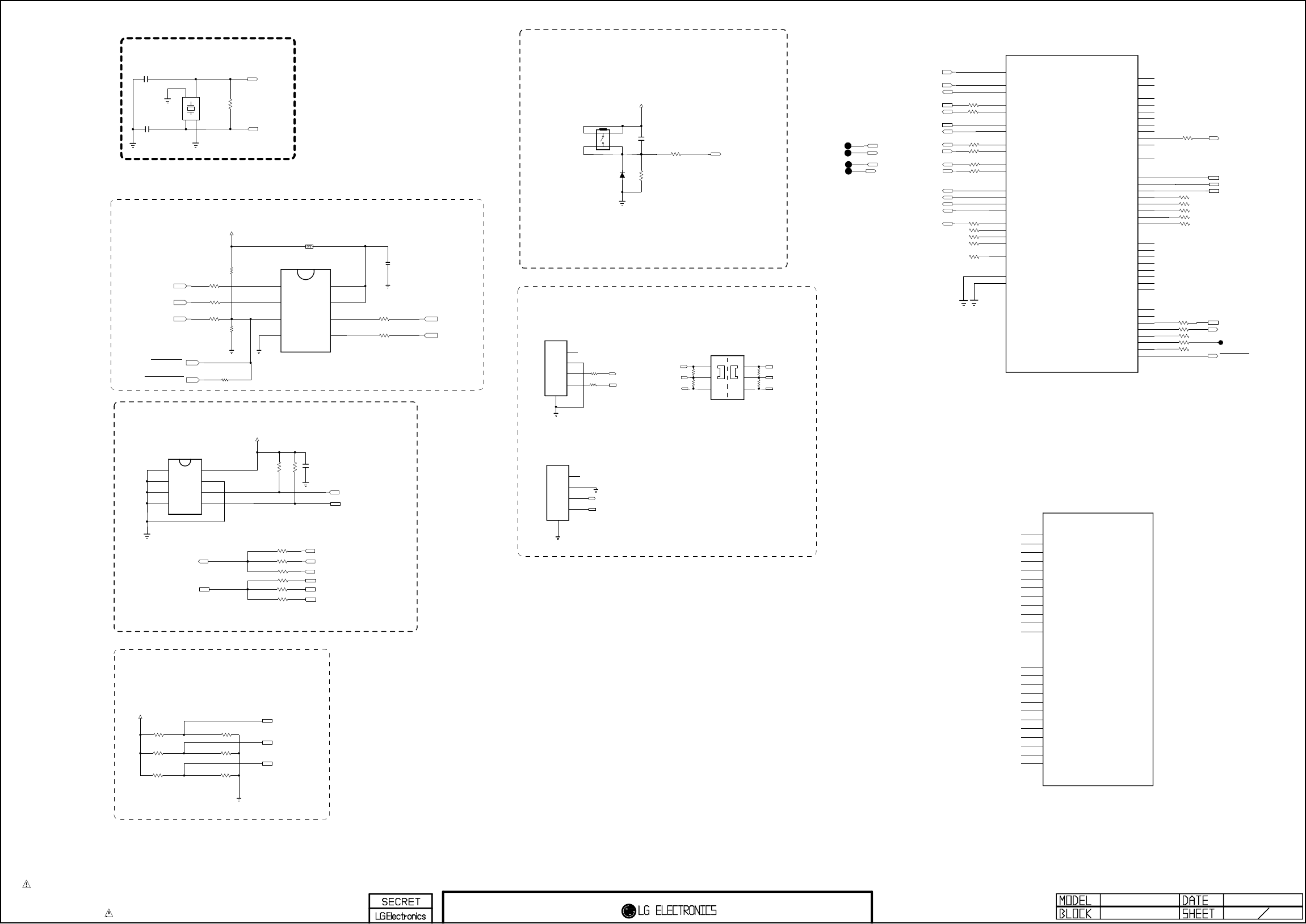

SPI_DI

SPI_DO

R1909

10K

+3.3V

SPI_CZ

L1900

MLB-201209-0120P-N2

SPI_CK

R1910

10K

OPT

C1901

0.1uF

25V

XIN_URSA

XO_URSA

IC2007

R1EX24256BSAS0A

3

A2

2

A1

4

VSS

1

A0

5

SDA

6

SCL

7

WP

8

VCC

+3.3V

C1900

0.1uF

25V

R1917

4.7K

R1918

4.7K

UART2_TX

I2CS_SDA

I2CS_SCL

R1936

0

R1946

0

SPI_CZ

SPI_CK

SPI_DI

SPI_DO

R1902

10K

R1908

10K

OPT

R1907

10K

OPT

R1901

10K

R1906

10K

OPT

R1900

10K

+3.3V

DIM0

DIM1

DIM2

DIM2

DIM1

DIM0

R1937

0

L_DIM_EN

I2CM_SCL_EEPROM

I2CM_SDA_EEPROM

I2CM_SDA_EEPROM

I2CM_SCL_EEPROM

I2CM_SCL_M_Port

I2CM_SCL_URSA

R1911

33

OPT

I2CM_SCL1_URSA

R1912

33

OPT

I2CM_SDA_URSA

I2CM_SDA1_URSA

I2CM_SDA_M_Port

I2CM_SDA1_URSA

R1913

33

R1915

33

I2CM_SCL1_URSA

I2CM_SDA_URSA

I2CM_SCL_URSA

R1914

33

R1916

33

R1945

33

OPT

R1950

33

OPT

R1940

33

OPT

R1935

33

OPT

R1951

33

OPT

R1941

33

OPT

R1942

33

OPT

R1933

33

OPT

R1931

33

OPT

R1932

33

OPT

R1934

33

OPT

R1920

33

R1919

33

R1903

33

R1904

33

URSA7_Reset

R1925

1M

XO_URSA

X1900

24MHz

4

GND_2

1

X-TAL_1

2

GND_1

3

X-TAL_2

XIN_URSA

+3.3V

SW1901

JTP-1127WEM

1 2

43

R1923

10K

D1900

100V

1N4148W

URSA7_Reset

C1902

22uF

10V

OPT

I2CS_SDA

R1958

0

URSA_MP

R1959

0

URSA_MP

SCL_M1_A SDA_M1_A

SCL2_+3.3V_DB

R1961

0

OPT

SDA2_+3.3V_DB

I2CS_SCL

SDA2_+3.3V_DB

R1960

0

OPT

SW1902

JS2235S

URSA_DEBUG

3

2

1

4

5

6

SCL2_+3.3V_DB

R1921

33

URSA_DEBUG

R1922

33

URSA_DEBUG

I2CM_SDA_M_Port

I2CM_SCL_M_Port

R1963

33

R1964

33

R1924

0

P1905

12507WS-04L

WAFER-STRAIGHT

1

2

3

4

5

P1908

12507WS-04L

WAFER-STRAIGHT

1

2

3

4

5

UART2_TX

R1929

33

UART1_TX

R1926

33

UART2_RX

R1927

33

UART2_RX

UART2_TX

UART1_RX

UART1_TX

UART1_RX

R1928

33

FLASH_WP

URSA7_stable

R1930 0

IC1901

MX25L3206EM2I-12G

3

WP#

2

SO/SIO1

4

GND

1

CS#

5

SI/SIO0

6

SCLK

7

HOLD#

8

VCC

R1944

33

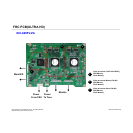

IC2500

LGE7410

RESET

AA28

XTALO

AM3

XTALI

AL3

I2CS_SDA

AJ22

I2CS_SCL

AH23

I2CM_SDA

AG24

I2CM_SCL/VSYNC_LIKE1

AG25

GPIO[0]/UART2_TX

E8

GPIO[1]/UART2_RX

D8

GPIO[2]/UART1_TX

D9

GPIO[3]/UART1_RX

E9

SPI_CZ

AE31

SPI_CK

AD30

SPI_DI

AD32

SPI_DO

AE32

INT_R21/GPIO[41]

AB29

INT_R20/GPIO[42]

AA29

GPIO[10]/PWM_DIM_IN[0]

AH25

GPIO[11]/PWM_DIM_IN[1]

AG26

IRE

F8

TESTPIN

AA26

GND_EFUSE

AA27

VSYNC_LIKE2

AH24

VSYNC_LIKE3

AJ24

SPI1_CK/PWM2/GPIO58

AE28

SPI1_DI/PWM3/GPIO59

AE29

SPI2_CK/PWM0/GPIO56

AF28

SPI2_DI/PWM1/GPIO57

AE27

SPI3_CK/DIM10/GPIO54

AG29

SPI3_DI/DIM11/GPIO55

AF27

SPI4_CK/DIM8/GPIO52

AG27

SPI4_DI/DIM9/GPIO53

AG28

VSYNC_LIKE/PWM5/GPIO40

AD27

DIM0/GPIO[32]

AH20

DIM1/GPIO[33]

AG20

DIM2/GPIO[34]

AJ21

DIM3/GPIO[35]

AH21

DIM4/GPIO[36]

AG21

DIM5/GPIO[37]

AG22

DIM6/GPIO[38]

AH22

DIM7/GPIO[39]

AG23

NC_21

E7

NC_22

F7

NC_23

D6

NC_24

D5

NC_25

E6

NC_26

E5

NC_27

F6

NC_28

F5

VX1T_HTPDN

AF4

VX1T_LOCKN

AE4

I2CM_SDA1

AF5

I2CM_SCL1

AG4

TGPIO12

AG5

3D_FLAG

AH4

TGPIO14

AH5

TGPIO15

AJ5

IC2500

LGE7410

GPIO[8]/HDMIRX_CEC

AH28

GPIO[9]/HDMIRX_HPD

AH29

GPIO[6]/DDCDA_CK

AJ27

GPIO[7]/DDCDA_DA

AJ28

HDMI_RXCP

AH32

HDMI_RXCN

AH31

HDMI_RX0P

AG32

HDMI_RX0N

AG30

HDMI_RX1P

AF30

HDMI_RX1N

AG31

HDMI_RX2P

AE30

HDMI_RX2N

AF31

GPIO[4]/HDMITX_CEC

AH26

GPIO[5]/HDMITX_HPD

AH27

HDMITX_SCL

AJ25

HDMITX_SDA

AJ26

HDMITX_CLKP

AL31

HDMITX_CLKN

AM31

HDMI_TX0P

AK31

HDMI_TX0N

AL32

HDMI_TX1P

AJ30

HDMI_TX1N

AK32

HDMI_TX2P

AH30

HDMI_TX2N

AJ31

FLASH_WP_U

R1939 0

OPT

C1903

8pF

C1904

8pF

FLASH_WP_U

R1905

1K

OPT

SPI Flash

I2C EEPROM

2013.03.18

U_UART,GPIO 20 22

Chip Config

Clock for URSA7

URSA Reset

Debug/ISP ADDR

Slabe (Debug Port:0XB4,ISP:0X98)

CHIP_CONF:{DIM2,DIM1,DIM0}

CHIP_CONF=3’d7:111:boot from SPI Flash

I2C_S Port

Debugging for URSA

I2C_M Port

EAX65309301

4MByte

Copyright © 2013 LG Electronics. Inc. All rights reserved.

Only for training and service purposes

LGE Internal Use Only