LD-14115-5

4-2

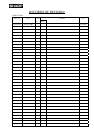

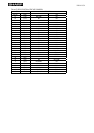

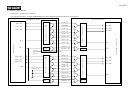

Interface block diagram

Using receiver

:

Contained in a control IC.

Corresponding Transmitter

:

THC63LVDM83R(THine electronics),DS90C383,DS90C383A(National semiconductor)

GA0~GA7

BA0~BA7

DEA

RA0~RA7

RB0~RB7

BB0~BB7

GB0~GB7

TTL parallel → LVDS

RAIN0+(5)

RAIN0-

(

6

)

8

8

8

PLL

8

8

8

Controller

PLL

LVDS → TTL parallel

LVDS → TTL parallel

PLL

PLL

RAIN1+(8)

RAIN1-(9)

RAIN2-

(

12

)

RBIN0+

(

5

)

RBIN0-

(

6

)

RBIN1+

(

8

)

RBIN1-(9)

RBIN2+

(

11

)

RBIN2-

(

12

)

RBCLKIN+

(

14

)

RBCLKIN-

(

15

)

8

8

8

8

8

8

DEA

RB0~RB7

BB0~BB7

GB0~GB7

Internal circuits

CLK

CLK

(Computer side)

A Port

B Port

(TFT-LCD side)

TxIN18~20

RAIN3+

(

17

)

RAIN3-(18)

RBIN3+

(

17

)

RBIN3-

(

18

)

RAIN2+(11)

RACLKIN+

(

14

)

RACLKIN-

(

15

)

TTL parallel → LVDS

RA0~RA7

BA0~BA7

GA0~GA7

DEB

DEB