1-8 (No.YA092B)

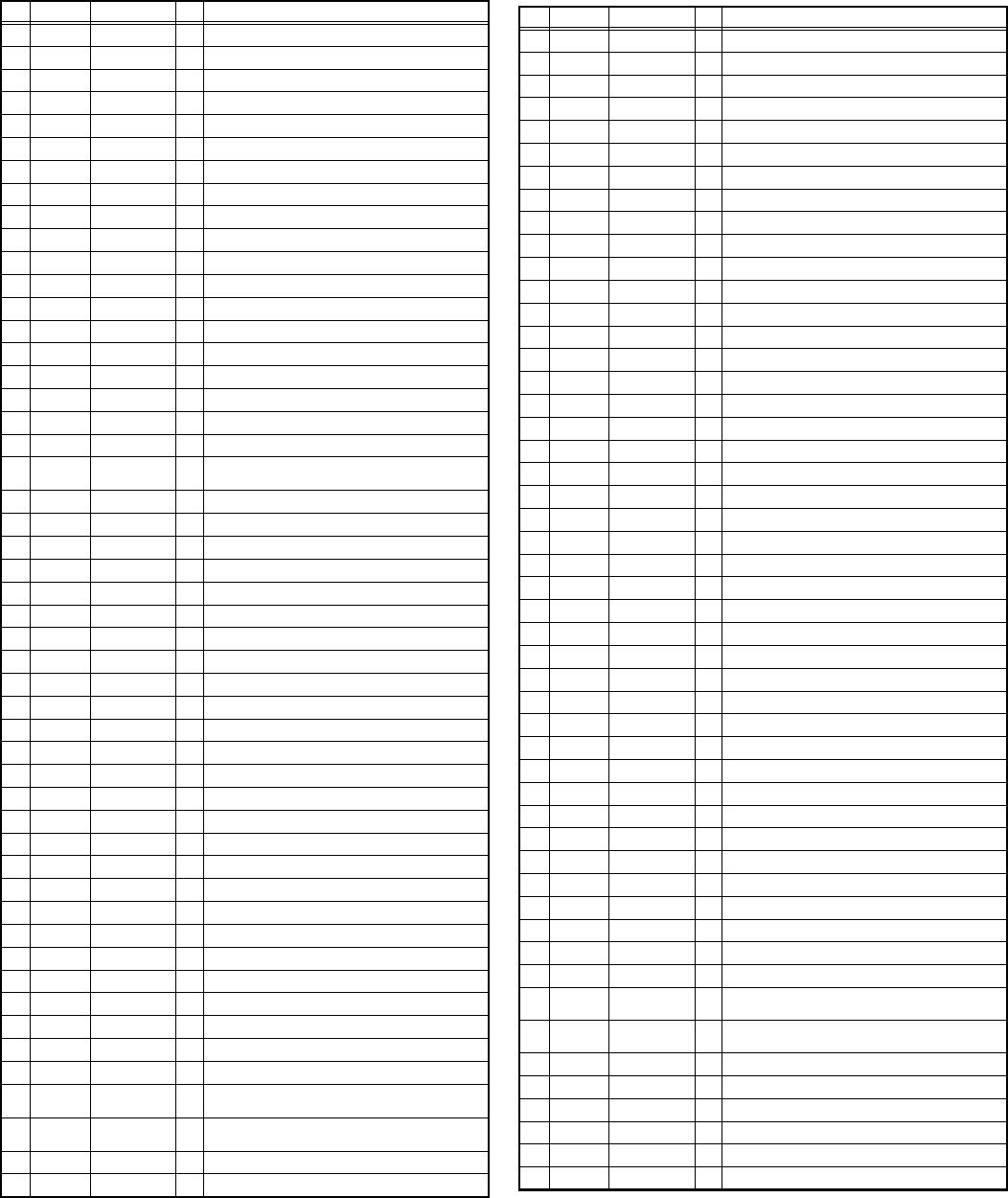

2.1.6 MAIN CPU PIN FUNCTION (IC7601 : M306V7FGF-088FP) [DIGITAL SIGNAL PWB ASS’Y]

Pin Port Pin name I/O Function

1 VHOLD1 VHOLD1 I Data slice for main screen closed caption

2 HFLT1 HFLT1 I/O LPF for main screen closed caption video input

3 P9.4 O Not used

4 P9.3 O Not used

5 P9.2 DIGRO O R [0] for OSD

6 P9.1 TB1IN I AC power for timer clock

7 P9.0 REMO I Remote control

8 BYTE BYTE I Data bus width select [L = 16bit (fixed)]

9 CNVss CNVss I CPU programming mode select [Normal = L]

10 P8.7 DIGGO O G [0] for OSD

11 P8.6 DIGBO O B [0] for OSD

12 RESET RESET I Reset for main CPU [Reset = L]

13 XOUT XOUT O System clock osillation (crystal) : 16MHz

14 Vss Vss - GND

15 XIN XIN I System clock osillation (crystal) : 16MHz

16 VccI VccI I 3.3V stand-by power supply

17 OSC1 OSC1 I Clock for OSD

18 OSC2 OSC2 O Not used : Clock for OSD

19 P8.3 INT1 I AV COMPULINK control

20 P8.2 INT0 I Request for sub(chassis) CPU communication

(serial data)

21 OUT1 OUT1 O Ys (blanking) for OSD

22 OUT2 OUT2 O YM (transparence) for OSD

23 P7.7 O Not used

24 P7.6 O Not used

25 P7.5 O Not used

26 P7.4 O Not used

27 P7.3 CTA2/RTS2 O Not used : Digital tuner control

28 P7.2 CLK2 O Not used : Digital tuner control

29 P7.1 RxD2 I Not used : Digital tuner control

30 P7.0 TxD2 O Not used : Digital tuner control

31 P6.7 SDA2 I/O Not used

32 DIGR1 DIGR1 O R [1] for OSD

33 DIGG1 DIGG1 O G [1] for OSD

34 DIGB1 DIGB1 O B [1] for OSD

35 P6.3 TxDO I Data receive (serial) for external programming

36 P6.2 RxDO O Data transmission (serial) for external programming

37 P6.1 CLKO I Clock for external programming

38 P6.0 RTSO O Busy for external programming [Operation = H]

39 P5.7 I Not used

40 P5.6 O Not used

41 HOLD HOLD I CPU programming mode select [Normal = H]

42 P5.4 O Not used

43 P5.3 O Not used

44 P5.2 O Not used

45 P5.1 O Not used

46 P5.0 WR O CPU programming mode select [Normal = L]

47 P4.7 MICON_TX O Data transmission for sub(chassis) CPU

communication (serial)

48 P4.6 MICON_RX I Data receive for sub(chassis) CPU communication

(serial)

49 P4.5 MI_CLK I Clock for sub(chassis) CPU communication (serial)

50 P4.4 O Not used

Pin Port Pin name I/O Function

51 P4.3 O Not used

52 P4.2 O Not used

53 P4.1 O Not used

54 P4.0 O Not used

55 P3.7 O Not used

56 P3.6 O Not used

57 P3.5 O Not used

58 P3.4 O Not used

59 P3.3 O Not used

60 P3.2 O Not used

61 P3.1 O Not used

62 HSYNC HSYNC I H. sync for OSD

63 P3.0 O Not used

64 VSYNC VSYNC I V. sync for OSD

65 P2.7 O Not used

66 P2.6 O Not used

67 P2.5 O Not used

68 P2.4 O Not used

69 P2.3 O Not used

70 P2.2 O Not used

71 P2.1 O Not used

72 P2.0 O Not used

73 P1.7 O Not used

74 P1.6 O Not used

75 P1.5 O Not used

76 P1.4 O Not used

77 P1.3 O Not used

78 P1.2 O Not used

79 P1.1 O Not used

80 P1.0 O Not used

81 P0.7 O Not used

82 P0.6 O Not used

83 P0.5 O Not used

84 P0.4 WAKE O Reset for sub(chassis) CPU

85 P0.3 CARD_DET I Not used : Card detection for ATSC digital tuner

86 P0.2 POWER_SW I Not used : Power switch (mechanical) detection

87 P0.1 SDA0 I/O Data for Inter IC (serial) bus control : memory

88 P0.0 SCL0 O Clock for Inter IC (serial) bus control : memory

89 P10.7 DIGR2 O R [2] for OSD

90 P10.6 DIGG2 O G [2] for OSD

91 P10.5 DIGB2 O B [2] for OSD

92 P10.4 O Not used

93 P10.3 KEY1 I Key scan data for front control button

(MENU/CH+/CH-) KEY2

94 P10.2 KEY0 I Key scan data for front control button

(VOL+/VOL-) KEY1

95 VHOLD2 VHOLD2 I Data slice for sub screen closed caption

96 HLF2 HLF2 I/O LPF for sub screen closed caption video input

97 CVIN2 CVIN2 I Video(Y) for sub screen closed caption

98 TVSETB TVSETB I Test terminal [L Fixed]

99 VCCE VCCE I 5V stand-by power supply

100 CVIN1 CVIN1 I Video(Y) for main screen closed caption