3 - 9 3 - 9

MELSEC-Q

3 SPECIFICATIONS

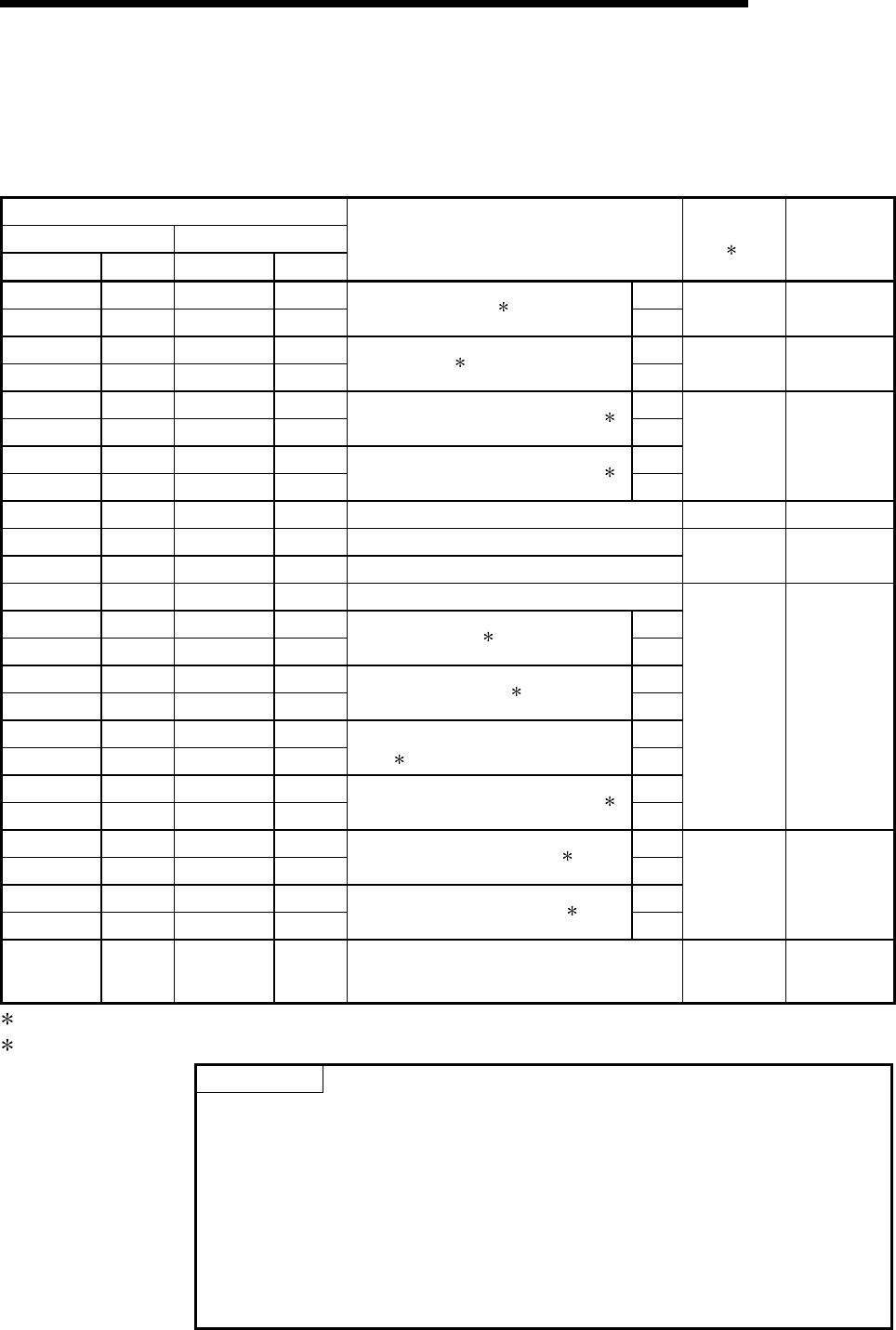

3.4 Buffer Memory Assignments

(1) Buffer memory assignment list

Buffer memory assignments for the QD62 (E/D) are listed in the table below.

For details on the buffer memories, refer to this section (2) to this section (12).

Address

CH1 CH2

Hexadecimal Decimal Hexadecimal Decimal

Set data

Initial value

1

Read/write

0H 0 20H 32 (L)

1H 1 21H 33

Preset value setting

2

(H)

0

Read/write

enabled

2H 2 22H 34 (L)

3H 3 23H 35

Present value

2

(H)

0 Read only

4H 4 24H 36 (L)

5H 5 25H 37

Coincidence output point set No. 1

2

(H)

6H 6 26H 38 (L)

7H 7 27H 39

Coincidence output point set No. 2

2

(H)

0

Read/write

enabled

8H 8 28H 40 Overflow detection flag 0 Read only

9H 9 29H 41 Counter function selection setting

AH 10 2AH 42 Sampling/periodic setting

0

Read/write

enabled

BH 11 2BH 43 Sampling/periodic counter flag

CH 12 2CH 44 (L)

DH 13 2DH 45

Latch count value

2

(H)

EH 14 2EH 46 (L)

FH 15 2FH 47

Sampling count value

2

(H)

10H 16 30H 48 (L)

11H 17 31H 49

Periodic pulse count previous

value

2

(H)

12H 18 32H 50 (L)

13H 19 33H 51

Periodic pulse count present value

2

(H)

0 Read only

14H 20 34H 52 (L)

15H 21 35H 53

Ring counter minimum value

2

(H)

16H 22 36H 54 (L)

17H 23 37H 55

Ring counter maximum value

2

(H)

0

Read/write

enabled

18H

to

1F

H

24

to

31

38

H

to

3F

H

56

to

63

System area — —

1: The initial values are set when the power is turned on or the CPU module is reset.

2: Read or write values in the 32-bit signed binary format. (Be sure to use two words at a time.)

POINT

(1) The system area and the areas not listed in the table are for the system and are

not available for users.

If they are written by user, the functions of the QD62(E/D) are not guaranteed.

(2) All data in the buffer memory of the QD62(E/D) are initialized when the

QD62(E/D) is powered on or the CPU module is reset.

For this reason, to save the necessary data, write/read the data to/from the

buffer memory by executing the FROM/DFRO/TO/DTO instructions in the

sequence program or performing auto refresh to the devices in the CPU

module.