— 35 —

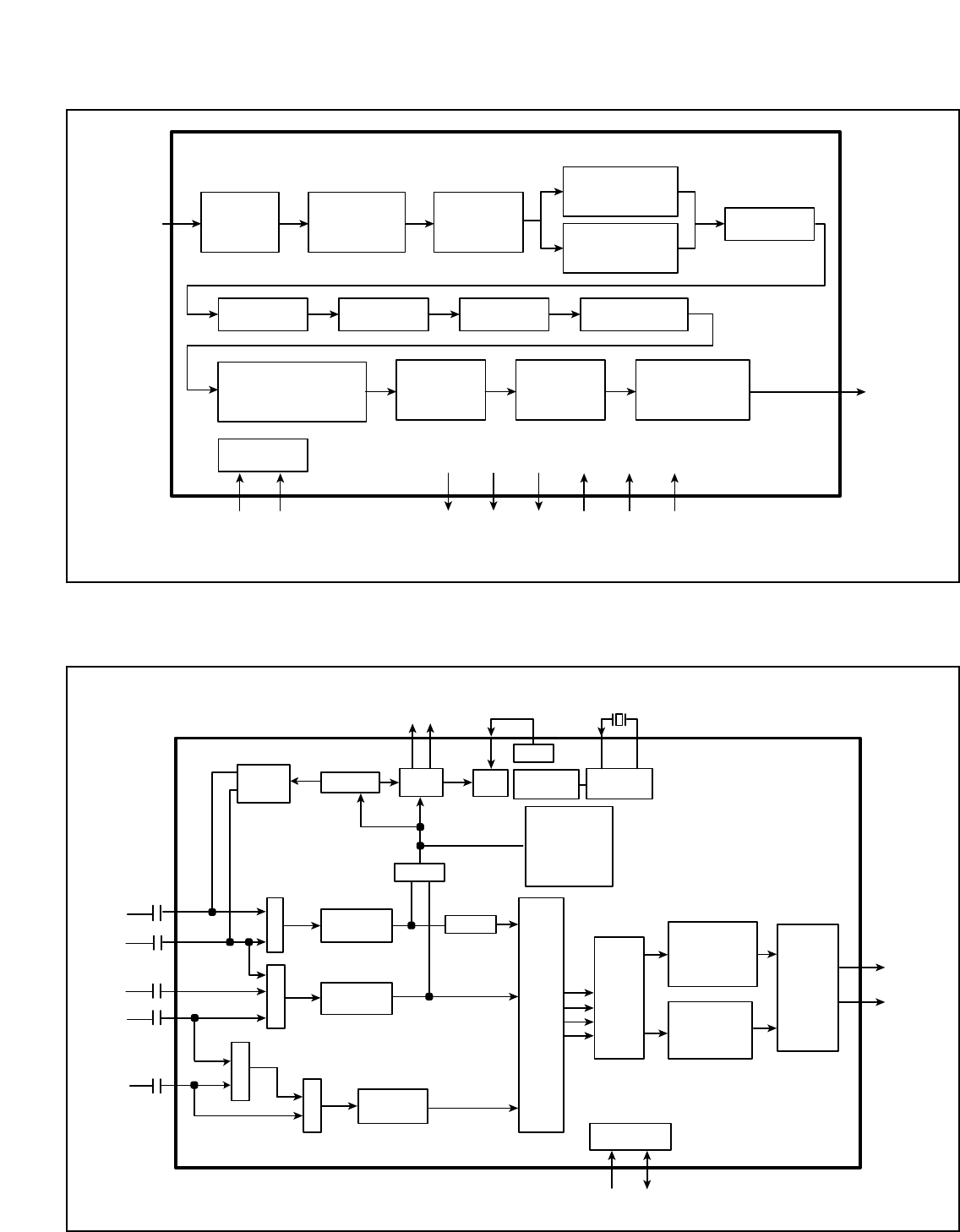

IP Converter/Screen Controller/LVDS Transmitter (IC7201)

IC BLOCK DIAGRAMS

LVDS

Outpu

t

656/601

Input

SCL

SDA OSD

H

OSD

V

OSD

CLK

OSD

R

OSD

G

OSD

B

656/601

Decoder

Sharpness

(Y Only)

γ

-Correct

Black-Expander

H-Scaling

(4/5)

Test

Pattern

OSD

Insert

LVDS

Transmitter

V-Scaling

Tint

I2C-Bus

Line Doubler

(for 20V)

Line Tripler

(for 15V)

Matrix Contrast

Brightness

Digital Decoder (IC2001)

CVBS

Sync Sep.

C

Cb

Cr

Reference

Clock

42M

X'tal

Vertical

Enhance

Delay Adjust

Contrast Adust

ACC

Color Decode

TINT Adjust

Color Adjust

ITU-R656

Encode

656/601

Format

HD/VD

Timing

LTI

Clock

Generate

D/A

X 8

Y

27M

8bit ADC

27M

8bit ADC

MPX

SW

27

M

10bit ADC

SW

SW

27M

→

4fsc

SW

78

81

86

88

94

3line

Comb.

Clamp

IIC-BUS

SCL SDA

ID1

S/N detection

CCD Slice

WSS

Macrovision

AGC

27 26

68 70 3 7 898