– 48 – – 49 –– 47 – – 50 –

KV-J14P2S/J51PF2S

RM-869

KV-J14P2S/J51PF2S

RM-869

KV-J14P2S/J51PF2S

RM-869

KV-J14P2S/J51PF2S

RM-869

Schematic diagrams

? C VM boards

Schematic diagram

A (2/2) board /

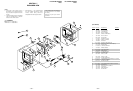

PRINTED WIRING BOARDS

C

[RGB OUT, DEFLECTION]

C BOARD WAVEFORMS

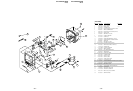

A Board IC300 TDA8374A (KV-J14P2S)

A Board IC300 TDA8375A (KV-J51PF2S)

– C Board – (KV-J14P2S)

– C Board – (KV-J51PF2S)

– VM Board – (KV-J51PF2S)

A Board IC351 TDA4665T-T/ V5-118

PAL/SECAMW-W

26Vp-p (H) SECAM : 148Vp-p (H)

NTSC PAL/SECAM

150Vp-p (H)

PAL/SECAMNTSC

150Vp-p (H) 140Vp-p (H)

NTSC

150Vp-p (H)

PAL : 154Vp-p (H)

PAL : 100Vp-p (H)

SECAM : 140Vp-p (H)

4

43

32

21

AGC FOR IF

· TUNER

54

53

TUNER

T. D.P.

· DEMODULATOR

VIF AMPLIFIER

49

48

AFC · S/H VIDEO AMPL.

POL

VIDEO IDENT

IDENT

AFC

POL

VIDEO MUTE

MUTE

SW

CVBS-SWITCH

13 17

SOUND

TRAP

6

SVHS-SWITCH

SW

10

ChrCVBS Y

11

S-VHS

38

CVBS OUT

TRAP

BAND-

PASS

PAL / NTSC

DECODER

4.4 3.6

36 35 34

SECAM REF.

3316

HUE

FILTER

TUNING

30 29

R-Y

B-Y

REF

DELAY ·

PEAKING

G-Y MATRIX ·

SAT. CONTROL

R-Y

B-Y

32 31

TDA 4661

SAT

OUT IN

Y

28 27

· OUTPUT

RGB-MATRIX

26

BL

25

B

24

G

· SWITCH

R

23

RGB-INPUT

21

20

19

R

G

B

22

BEAM DUPR.

BACK-

STABILISER

CONTR

BRI

WHITE P.

BL. CURRENTCURRENT

18

VERTICAL

GEOMETRY

51

52

46

47

V-OUT POS.

V-OUT NEG.

EW-

GEOMETRY

45

50

EW-DRIVE

EHT

H/V DIVIDER

SYNC SEP.

· 1st LOOP

SEPARATOR

VERT. SYNC

VCO ·

CONTROL

· HOR. OUT

2nd LOOP

42 41 39 40

HOR. DRIVEBV

44 14 9 5 12 37

12C-BUS

TRANSCEIVER

78

SCL SDA

CONTROL DAC 's

17 x 6-BIT 's

2 x 4-BIT 's

IF-IN

4

3

REF

SIGNAL

CLAMPING

LINE

MEMORY

SAMPLE-

AND-

HOLD

LP

±(R-Y)

16

11

±(R-Y)

±(B-Y)

12

14

±(B-Y)

LP

HOLD

AND-

SAMPLE-

MEMORY

LINE

CLAMPING

SIGNAL

pre-amplifiers

addition

stages

output

buffers

colour-difference

output signals

SANDCASTLE

DETECTOR

DETECTOR

PHASE

FREQUENCY

9

analog supply

5

colour-difference

input signals

V

P1

sandcastle

pulse input

DIVIDER

BY 192

LP

5MHz

CCO

DIVIDER

BY 2

1

digital supply

10

GND1

3 4, 8

GND2

2 n.c.

n.c.6

n.c.13

n.c.15

3MHz shifting clock

7 i.c.

TDA4665

P2

V

MED848

VM

[VM OUT]