5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

DI_SCL

DI_SDA

DEINTDONE

MEM_DQM_U

MEM_CAS_N

MEM_WE_N

MEM_CS_N

MEM_RAS_N

MEM_CLK

MEM_A[0..11]

MEM_DQM_L

MEM_DQ[0..79]

MEM_BS

V_VSYNC

V_ACTIVE

V_CLK

V_HSYNC

V_IN[0..15]

RESET_DVDO

DI_VSYNC

D_VSYNC

DIN_CLK

DI_HSYNC

DI_27M_CLK

D_HSYNC

DI_IN[2..9]

D_INA[0..23]

OP_VSYNC

OCLK_OUT

OP_FIELD

OP_HSYNC

OP_ENABLE

OP_A[0..23]

CPU_D[0..7]

RM1_WR_N

CPU_A[0..7]

RM1_CS_N

RM1CLKIN

DVI_ACTDATA

MUX_SEL_Q

RM1_IRQ

POWER

POWER

POWER

LAMPLIT

LAMPLIT

DMD_SCL

DMD_SDA

SII141_PDO

TRIGGER

RM1_RST_N

MUX_SEL

SDA

SCL

MCURESET

RESET_N

CPU_RXD0

CPU_TXD0

MUX_SEL_P

MUX_BUFFER

MUX_SEL

CPU_RD_N

RM1_RST_N

SII141_PDO

CPU_D[0..7]

TRIGGER

CPU_PCS0_N

MCURESET

CPU_WR_N

RESETVCC

WRITE_PROT

CPU_RD_N

DLP_SPARE

CPU_A1

CPU_A3

CPU_A2

CPU_A4

IR

SCL

KEY_LED0

SDA

KEYPAD[0..9]

DLP_RESETZ

KEY_LED1

SDA

SCL

POWERON

KEY_LED2

IR

DLP_RST

LAMP_PROTECT

FAN_CTRL

BACKLIGHT_CTRL

SYNCVALID

BALLAST_CTRL

SYNCVALID

BALLAST_CTRL

DVI_SCDT

DVI_SCDT

DMD_SDA

DMD_SCL

BACKLIGHT_CTRL

SPAREI

SPAREO

SPAREI

SPAREO

+3VA

+1_8V+3VA

+5VA+3VA

+3VA

+12VA +5VS+3VA +3VS+5VA

+12VA +3VA+5VA+5VS +1_8V

+1_8V

+12VA

+5VA

+5VS

+3VA

+3VS

+3VS

+5VS+3VS +12VA

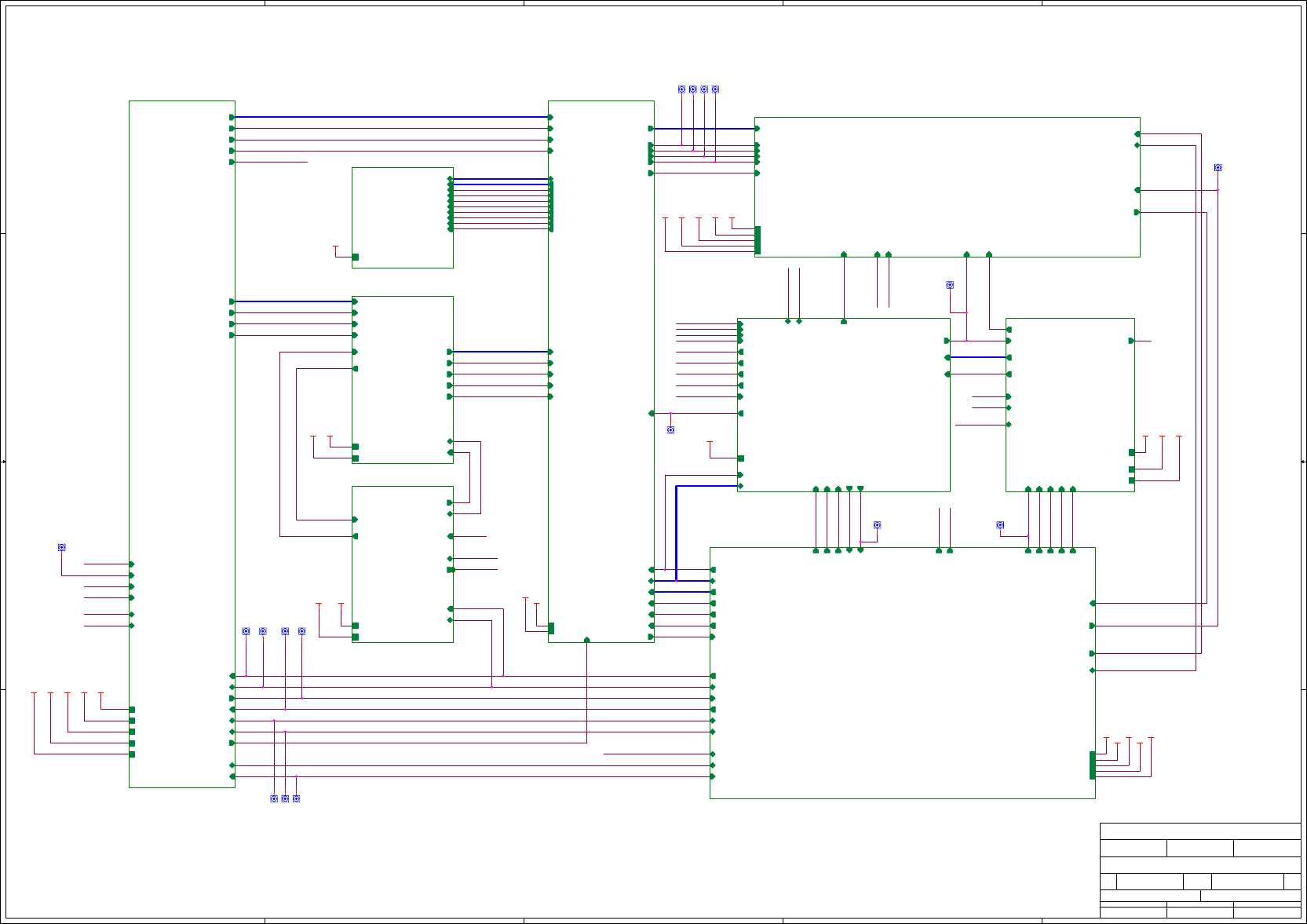

Title

Size Document Number Rev.

Date: Sheet

of

Project Code

Reviewed By Approved By

Prepared By

Model Name

PCB P/N

PCB Rev.

Benq Corporation

OEM/ODM Model Name

99.J5877.R22-C3-304-001

MAIN BOARD

1

10

COLIN CHANG BEN CHEN

48.J5801.S02

S02

ANGEL HU

<Size>

HT720G

99.J5877.001

0

Thursday, January 16, 2003

NA

DLP

Connector/POWER

CPU

SDRAM 64MBit x 3

8_SDRAM 64MBit x 3

+3VA

MEM_DQ[0..79]

MEM_CLK

MEM_RAS_N

MEM_CAS_N

MEM_BS

MEM_A[0..11]

MEM_WE_N

MEM_CS_N

MEM_DQM_L

MEM_DQM_U

RM1

4_RM1

MEM_DQ[0..79]

OP_VSYNC

OP_HSYNC

OP_ENABLE

DIN_CLK

D_VSYNC

D_HSYNC

D_INA[0..23]

CPU_D[0..7]

RM1_RST_N

RM1CLKIN

V_IN[0..15]

V_VSYNC

V_HSYNC

V_ACTIVE

VCLK

RM1_CS_N

RM1_WR_N

CPU_RD_N

+1_8V

+3VA

OCLK_OUT

MEM_RAS_N

MEM_WE_N

MEM_DQM_U

MEM_BS

MEM_CAS_N

MEM_CS_N

MEM_DQM_L

RM1_IRQ

MEM_CLK

OP_A[0..23]

MEM_A[0..11]

OP_FIELD

CPU_A[0..7]

DVI_ACTDATA

TP20

E1

1

TP3

E1

1

TP8

E1

1

MCU503 Controller

3_MCU503 Controller

+5VA

SDA

SCL

DI_SDA

DI_SCL

MCURESETRESET_DVDO

+3VA

DEINTDONE

DMD_SDA

DMD_SCL

TP1

E1

1

TP4

E1

1

KEYPAD&THERMAL_CONNECTOR

10_KEYPAD&THERMAL_CONNECTOR

IR

+5VS

KEY_LED0

KEY_LED1

KEY_LED2

KEYPAD[0..9]

POWERON

LAMP_PROTECT

FAN_CTRL

DLP_RESETZ

SCL

SDA

+3VS

DLP_RST

+12VA

BACKLIGHT_CTRL

TP6

E1

1

80 Pin Connector to DLP

7_100 Pin Connector to DLP/POWE

+5VA

+3VA

OCLK_OUT

OP_ENABLE

OP_VSYNC

+12VA

OP_A[0..23]

OP_HSYNC

DLP_RESETZ

DMD_SCL

DMD_SDA

LAMPLIT

POWERON

POWER

+5VS

+3VS

OP_FIELD

DLP_SPARE

SYNCVALID

BALLAST_CTRL

TP11

E1

1

TP9

E1

1

TP17

E1

1

TP18

E1

1

TP16

E1

1

TP5

E1

1

TP13

E1

1

TP15

E1

1

CPU_FLASH_SRAM

5_CPU_FLASH_SRAM

CPU_D[0..7]

+3VS

RM1_IRQ

CPU_TXD0

CPU_RXD0

RM1CLKIN

RM1_CS_N

RESET_N

SDA

SCL

+5VS

CPU_RD_N

CPU_PCS0_N

RM1_WR_N

WRITE_PROT

LAMPLIT

IR

DLP_RST

FAN_CTRL

POWER

MUX_BUFFER

MUX_SEL_P

KEY_LED0

KEY_LED1

KEY_LED2

+12VA

+5VA

+3VA

RESETVCC

CPU_A[0..7]

BACKLIGHT_CTRL

MUX_SEL_Q

CPU_WR_N

BALLAST_CTRL

SYNCVALID

DMD_SCL

DMD_SDA

TP19

E1

1

120-Pin B2B Connectors

1_120Pin B2B Connectors

D_INA[0..23]

D_VSYNC

D_HSYNC

DIN_CLK

SDA

SCL

DI_IN[2..9]

DI_27M_CLK

DI_VSYNC

DI_HSYNC

MUX_SEL

+3VA

+5VA

DVI_ACTDATA

SII141_PDO

CPU_RXD0

CPU_TXD0

+12VA

+1_8V

MUX_SEL_P

MUX_BUFFER

TRIGGER

+5VS

RM1_RST_N

MUX_SEL_Q

IR

DVI_SCDT

SPAREI

SPAREO

Sil503_Deinterlacer

2_Sil504_Deinterlacer

DI_IN[2..9]

V_IN[0..15]

V_ACTIVE

V_VSYNC

V_HSYNC

DI_27M_CLK

DI_SDA

DI_SCL

RESET_DVDO

+3VA

VCLK

+1_8V

DI_HSYNC

DI_VSYNC

DEINTDONE

TP2

E1

1

I/O

6_I/O

CPU_D[0..7]

CPU_PCS0_N

SII141_PDO

RESET_N

CPU_WR_N

+3VS

MUX_SEL

WRITE_PROT

RM1_RST_N

POWERON

CPU_A1

CPU_A2

MCURESET

TRIGGER

RESETVCC

CPU_RD_N

CPU_A3

CPU_A4

KEYPAD[0..9]

DLP_SPARE

LAMP_PROTECT

DVI_SCDT

SPAREI

SPAREO

TP7

E1

1