5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

FLDATA[0..15]FLDATA[0..15]

FLDATA14

FLDATA11

FLDATA2

FLDATA1

FLDATA12

FLDATA7

FLDATA6

FLDATA15

FLDATA10

FLDATA13

FLDATA5

FLDATA9

FLDATA8

FLDATA4

FLDATA0

FLDATA3

OCLKA1

ARMTEST1

ARMTEST2

MOSCEN

MOSC

MCRYSTALEN

PWM0

PWM1

IDO25

DIO31

FLADDR18

FLADDR17

FLADDR16

FLADDR15

FLADDR14

FLADDR13

FLADDR12

FLADDR11

FLADDR10

FLADDR9

FLADDR8

FLADDR7

FLADDR6

FLADDR5

FLADDR4

FLADDR3

FLADDR2

FLADDR1

FLADDR0 FLADDR18

FLADDR17

FLADDR16

FLADDR15

FLADDR14

FLADDR13

FLADDR12

FLADDR10

FLADDR9

FLADDR8

FLADDR7

FLADDR6

FLADDR5

FLADDR4

FLADDR3

FLADDR2

FLADDR1

FLADDR0

FLADDR11

FLADDR[0..18]

FLDATA0

FLDATA1

FLDATA2

FLDATA3

FLDATA4

FLDATA5

FLDATA6

FLDATA7

FLDATA8

FLDATA9

FLDATA10

FLDATA11

FLDATA12

FLDATA13

FLDATA14

FLDATA15

DIO24

TSTPNT3

TSTPNT2

TSTPNT1

TSTPNT0

VDDMOSC

FL_OEZ

FL_WEZ

FL_CSZ

PUM_ARSTZ

P3P3V

P5V

DDP2P5V

P3P3V

DDP3P3V

DDP3P3V

DDP3P3V

SR16MODE0

SR16ADDR3

SR16OEZ

SR16ADDR0

SCP_CLK

SR16SEL0

SCP_DI

SCP_DO

SR16STROBE

SR16SEL1

SR16ADDR2

SR16MODE1

SR16ADDR1

OCLKA

EXT_ARSTZ

SCL_D

OCLKA

CLKIN

DRCGPDZ

DADSELZ

SCPDO

MTRPWM

DMDSPARE0

DMDSPARE1

MTRRSTZ

MTRSELZ

MTRCLK

MTRDATA

DADINTZ

MTRDMUX

DMDRSTZ

DMDSELZ

SDA_D

DMDSPARE0

DMDSPARE1

SCPDI

SCPCLK

CWINDEX

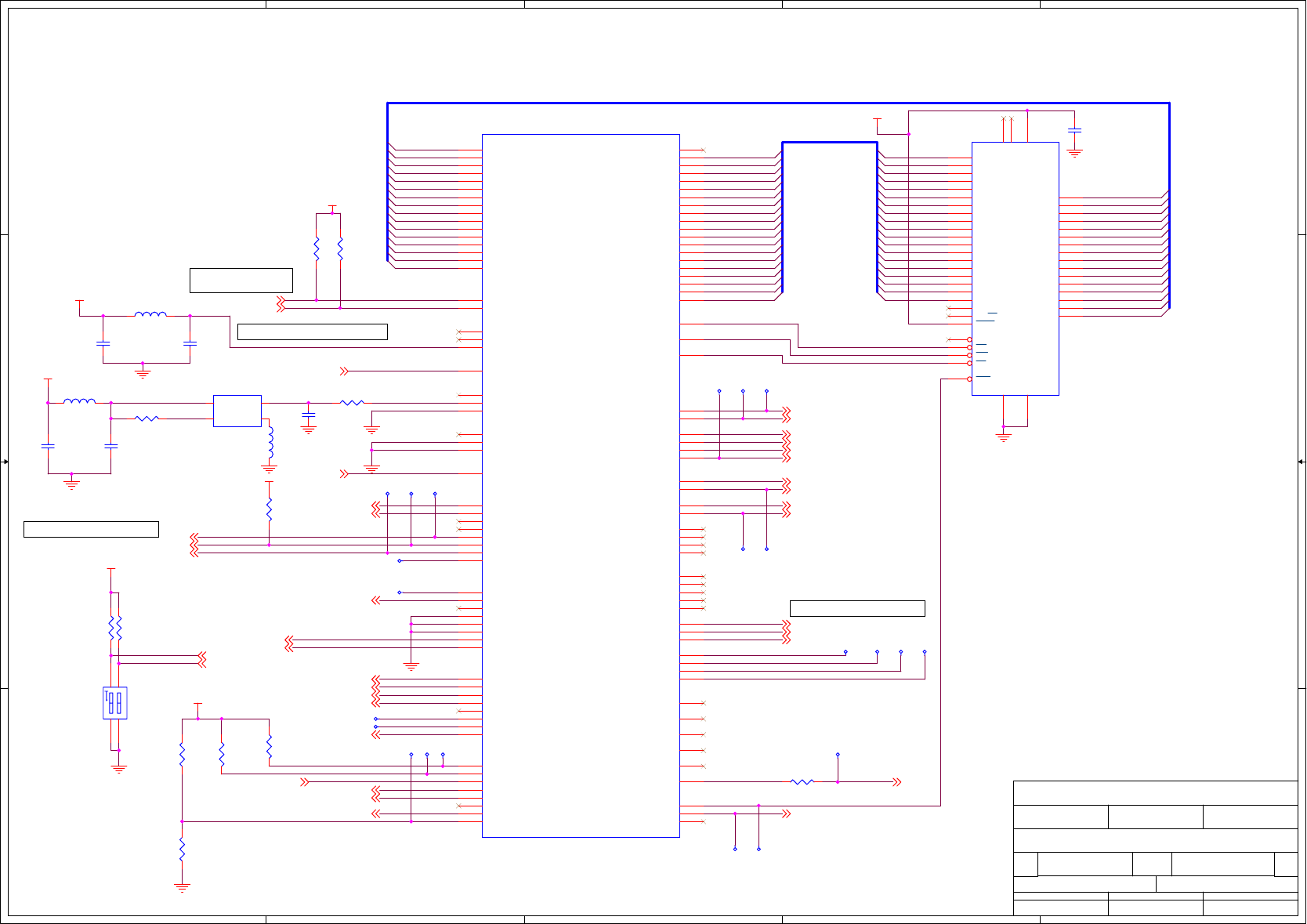

Title

Size Document Number Rev.

Date: Sheet

of

Project Code

Reviewed By Approved By

Prepared By

Model Name

PCB P/N

PCB Rev.

Benq Corporation

OEM/ODM Model Name

99.J5877.R22-C3-304-002

DMD BOARD

28

ALEX HY TSENG BEN CHEN

48.J5802.S01

S01

ANGEL HU

<Size>

HT720G

99.J5877.001

0

Tuesday, January 14, 2003

NA

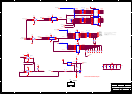

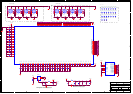

DDP1010 Flash, Micro, Clocks, DAD1000 Control

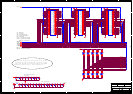

FLASH

DDP1010

IIC Bus (open drain)

Minimize Noise on PLL_VCCA

Master Clock (100MHz)

Pixel Clock (74.25MHz) from Scalar

(To MUSTANG)

(To SSI Motor)

(To DAD1000)

SERIES CONTROL PORT 1

(To DAD1000)

SERIES CONTROL PORT 0

50MHz Clock

(v-sync, delay CWI, spoketest for debug)

(Pin 14 should be disconnected from P3P3V)

(To DAD1000)

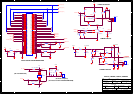

68.00129.0D1

TP32

C19

0.1U Z

R11

10K

C31

22P J

TP38

R12

1K

R15

22

TP39

TP45

R115

10K

TP46

C18

0.1U Z

TP40

TP47

R116

NC_R0603

R7

10K

TP48

TP28

TP41

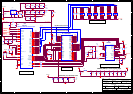

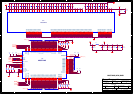

Micro, Clocks ,SR16 and Flash interface

U2B

DDP1010

FLDATA0

AG26

FLDATA1

AH26

FLDATA2

AJ26

FLDATA3

AF25

FLDATA4

AG25

FLDATA5

AJ25

FLDATA6

AJ24

FLDATA7

AF24

FLDATA8

AG24

FLDATA9

AH24

FLDATA10

AF23

FLDATA11

AG23

FLDATA12

AG22

FLDATA13

AJ22

FLDATA14

AF20

FLDATA15

AJ21

FLADDR19

AH7

FLADDR18

AF8

FLADDR17

AG8

FLADDR16

AF9

FLADDR15

AG9

FLADDR14

AH9

FLADDR13

AG10

FLADDR12

AJ10

FLADDR11

AG13

FLADDR10

AH13

FLADDR09

AJ14

FLADDR08

AF15

FLADDR07

AJ15

FLADDR06

AJ17

FLADDR05

AH17

FLADDR04

AH18

FLADDR03

AG19

FLADDR02

AH20

FLADDR01

AJ20

FLADDR0

AG20

FL_OE

AH27

FL_WE

AJ27

FL_CS

AF19

SR16STRB

V2

SR16OEZ

W3

SR16ADDR0

U2

SR16ADDR1

U1

SR16ADDR2

R1

SR16ADDR3

R4

SR16MODE0

P1

SR16MODE1

N2

DMDBIN0

N3

DMDBIN1

K1

DMDBIN2

K3

DMDBIN3

J3

SR16SEL0

Y1

SR16SEL1

Y2

SR16VCCEN

AB1

DMDVCCEN

Y4

VCC2EN

AA1

VBIASEN

Y3

VRSTEN

W4

SCP1_CLK

AF1

SCP1_DO

AF2

SCP1_DI

AF3

TSTPNT0

A20

TSTPNT1

C20

TSTPNT2

D19

TSTPNT3

A21

OCLKF

J2

OCLKE

H3

OCLKD

F1

OCLKC

E1

OCLKB

D1

OCLKA

E3

PUM_ARSTZ

C1

EXT_ARSTZ

D2

EXT_ARST

D3

SDA0

AH23

SCL0

AF22

APLLMD0

AF28

APLLMD1

AG28

PLL_VCCA

AG29

MOSCN

F3

MOSC

F2

MCRYSTALEN

G4

POSCN

G3

POSC

G2

PCRYSTALEN

H4

WCLK

T26

DIO0

AB28

DIO1

AA26

DIO2

AB27

DIO3

AB26

DIO4

AC28

DIO5

AC27

DIO6

AC26

DIO7

AD28

DIO8

AD27

DIO9

AD29

DIO10

AE28

DIO11/ASICID0

AE29

DIO12/ASICID1

AE27

DIO13/ASICID2

AE26

DIO14

AF29

DIO15

AH3

DIO16

AG4

DIO17

AH4

DIO18

AJ4

DIO19

AF5

DIO20

AG5

DIO21

AH6

DIO22

AF7

DIO23

AG7

DIO24

AB3

DIO25

AB4

DIO26

AC2

DIO27

AC3

DIO28

AC4

DIO29

AD2

DIO30

AD3

DIO31

AD4

COSC

AF27

R10

39.2F

SW1

6240019001

1

2

4

3

R13

1.33KF

TP34

TP29

TP1

L5

120 OHM

TP26

C21

0.1U Z

R8

10K

C20

0.1U Z

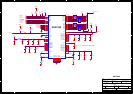

Y1

100MHZ

VCC

4

GND

2

OUT

3

OE

1

TP35

TP30

R14

1.33KF

TP2

C17

0.1U Z

TP27

L4

120 OHM

R113

10K

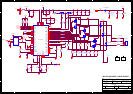

AM29LV800BB-120EC

U3

29LV800BB-90EC

7229800219

D0

29

D1

31

A0

25

D2

33

D3

35

A1

24

D4

38

D5

40

A2

23

D6

42

D7

44

A3

22

A4

21

A5

20

A6

19

A7

18

A8

8

A10

6

A11

5

A12

4

A13

3

A14

2

A15

1

A16

48

CE

26

A17

17

OE

28

WE

11

VSS

27

VCC

37

NC

13

VSS

46

RST

12

A18

16

D8

30

D9

32

D10

34

D11

36

D12

39

D13

41

D14

43

D15/A-1

45

NC

14

BYTE

47

RY/BY

15

A9

7

NC

9

NC

10

L19

220OHM

TP36

TP31

TP37

TP33

R114

10K