5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

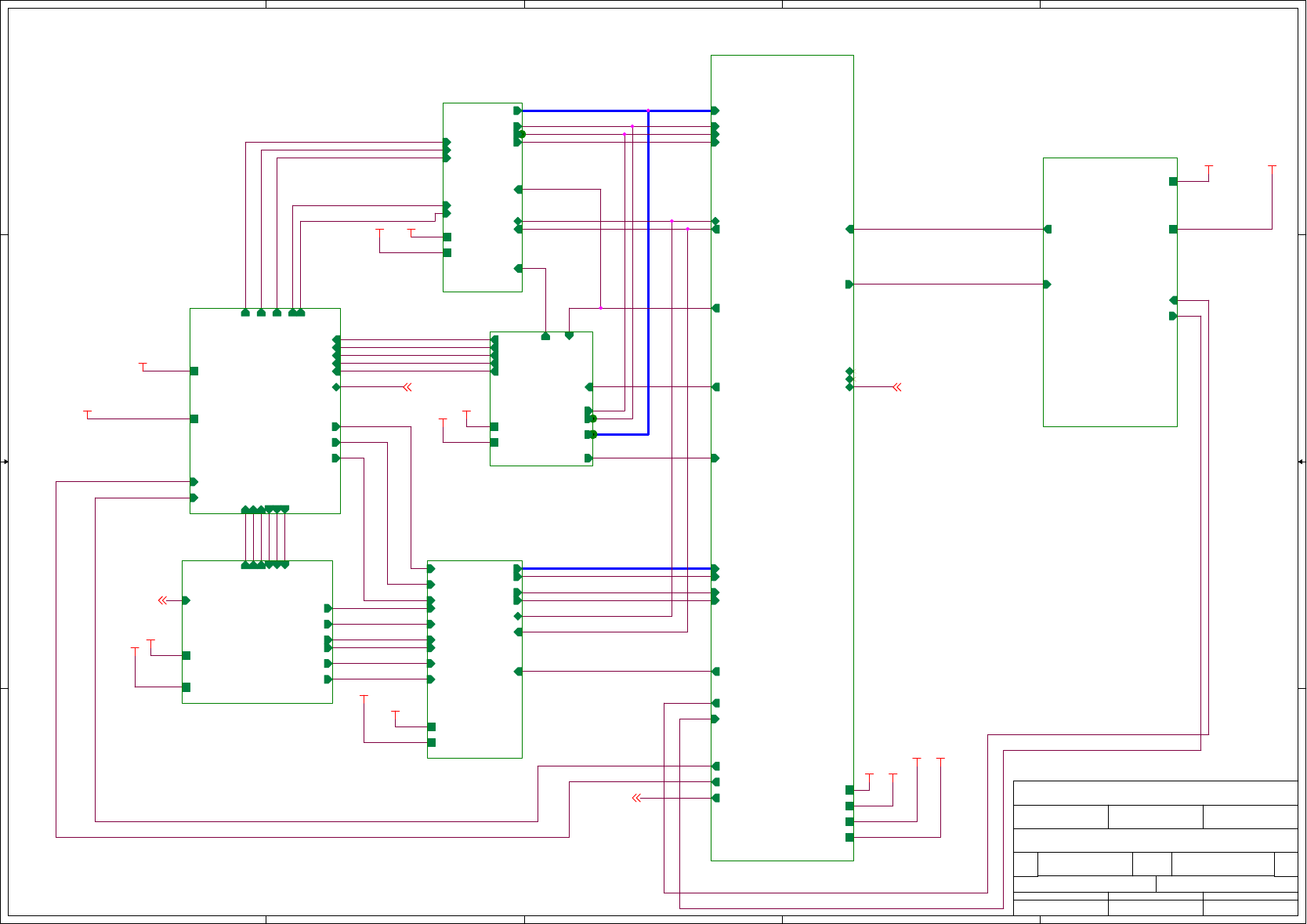

C

COMPOSITE

Y

Y/R

PB/G

VSYNC

Y_RCA

Cb_RCA

Cr_RCA

PC_BLUE

PC_RED

PC_VS

PC_GREEN

PbCbB

PC_HS

YpYcG

O_COMP_Y

O_COMP_CB

O_COMP_CR

PR/B

HSYNC

PrCrR

L_Y_G

L_Pb

L_Pr

DVI_CLK

SCL

DI_IN[2..9]

CPU_TXD0

DI_27M_CLK

DIN_CLK

DI_VSYNC

DVI_SCDT

SCL

D_HSYNC

CPU_RXD0

DI_HSYNC

SDA

DVI_ACTDATA

RESET_DEC

SDA

IR

D_INA[0..23]

MUX_SEL

TRIGGER

DVI_PDO

MUX_SEL_P

D_VSYNC

+5V_AD

+3VD

+5V_AD

+3VD

+5V_AD

+5V_AD

+12VA

+12VA+5VS

+5VS

+5V_MUX

+5V_MUX

+5V_AD

+5V_AD

+3VD

+3VD

MUX_BUFFER

MUX_BUFFER

MUX_SEL_Q MUX_SEL_Q

Title

Size Document Number Rev.

Date: Sheet

of

Project Code

Reviewed By Approved By

Prepared By

Model Name

PCB P/N

PCB Rev.

Benq Corporation

OEM/ODM Model Name

99.J5877.R22-C3-304-004

CONNECTOR BOARD

18

ALEX HY TSENG BEN CHEN

48.J5810.S02

S02

ANGEL HU

<Size>

HT720G

99.J5877.001

0

Monday, February 17, 2003

NA

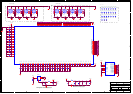

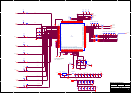

120-Pin B2B Connectors

7_120Pin B2B Connector

D_INA[0..23]

D_VSYNC

D_HSYNC

DIN_CLK

SDA

SCL

DI_IN[2..9]

DI_27M_CLK

DI_VSYNC

DI_HSYNC

MUX_SEL

CPU_RXD0

CPU_TXD0

RESET_DEC

+5V_AD

+3VD

+12VA

IR

TRIGGER

+5VS

MUX_SEL_Q

MUX_SEL_P

SPAREO

SPAREI

MUX_BUFFER

DVI_PDO

DVI_ACTDATA

DVI_SCDT

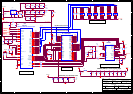

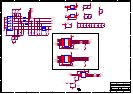

Video Inputs

2_Video Inputs

Y

C

COMPOSITE

+5V_AD

+5V_MUX

Y1

CB1

CR1

MUX_BUFFER

O_COMP_Y

O_COMP_CB

O_COMP_CR

L_Y_G

L_Pb

L_Pr

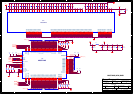

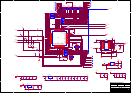

DVI

8_DVI INPUT&RECEIVER

PC_RED

PC_BLUE

PC_GREEN

PC_HS

PC_VS

D_INA[0..23]

D_VSYNC

D_HSYNC

DVI_PDO

+5V_AD

+3VD

DVI_ACTDATA

DVI_CLK

DVI_SCDT

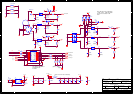

Graphics_ADC_AD9883

3_Graphics ADC AD9883

+5V_AD

+3VD

SDA

SCL

D_VSYNC

D_HSYNC

DIN_CLK

D_INA[0..23]

Y/R

PR/B

PB/G

VSYNC

HSYNC

DVI_CLK

DVI_PDO

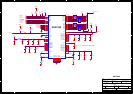

Video Decoder SAA7118E

5_Video Decoder SAA7118E

DI_27M_CLK

RESET_DEC

DI_IN[2..9]

SCL

SDA

+3VD

Y

C

PrCrR

PbCbB

YpYcG

COMPOSITE

DI_VSYNC

DI_HSYNC

+5V_AD

CR1

CB1

Y1

Trigger/3D/Thermal/RS232

6_Trigger/3D/Thermal/RS232

+12VAIR

CPU_TXD0

CPU_RXD0

TRIGGER

+5VS

Graphics_Inputs

1_Graphics Inputs

Y/R

PB/G

PR/B

MUX_SEL

+5V_AD

+5V_MUX

MUX_SEL_P

YpYcG

PbCbB

PrCrR

HSYNC

VSYNC

MUX_SEL_Q

PC_VS

PC_HS

PC_GREEN

PC_RED

PC_BLUE

O_COMP_CR

O_COMP_CB

O_COMP_Y

L_Y_G

L_Pb

L_Pr