Philips Semiconductors Product data sheet

SCC2691Universal asynchronous receiver/transmitter (UART)

2006 Aug 04

19

MASTER STATION

TxD

TRANSMITTER

ENABLED

TxRDY

(SR2)

CSN

(WRITE]

PERIPHERAL STATION

RxD

RECEIVER

ENABLED

RxRDY

(SR0)

RDN/WRN

ADD#1 1 D0 0 ADD#2 1

BIT 9 BIT 9 BIT 9

BIT 9 BIT 9 BIT 9 BIT 9 BIT 9

MR1[4:3] = 11

MR1[2] = 1

ADD#1 MR1[2] = 0 D0

MR1[2] = 1 ADD#2

0 ADD#1 1 D0 0 ADD#2 1 0

MR1[4:3] = 11

ADD#1

D0

SD

S = STATUS

D = DATA SD

ADD#2

SD00130

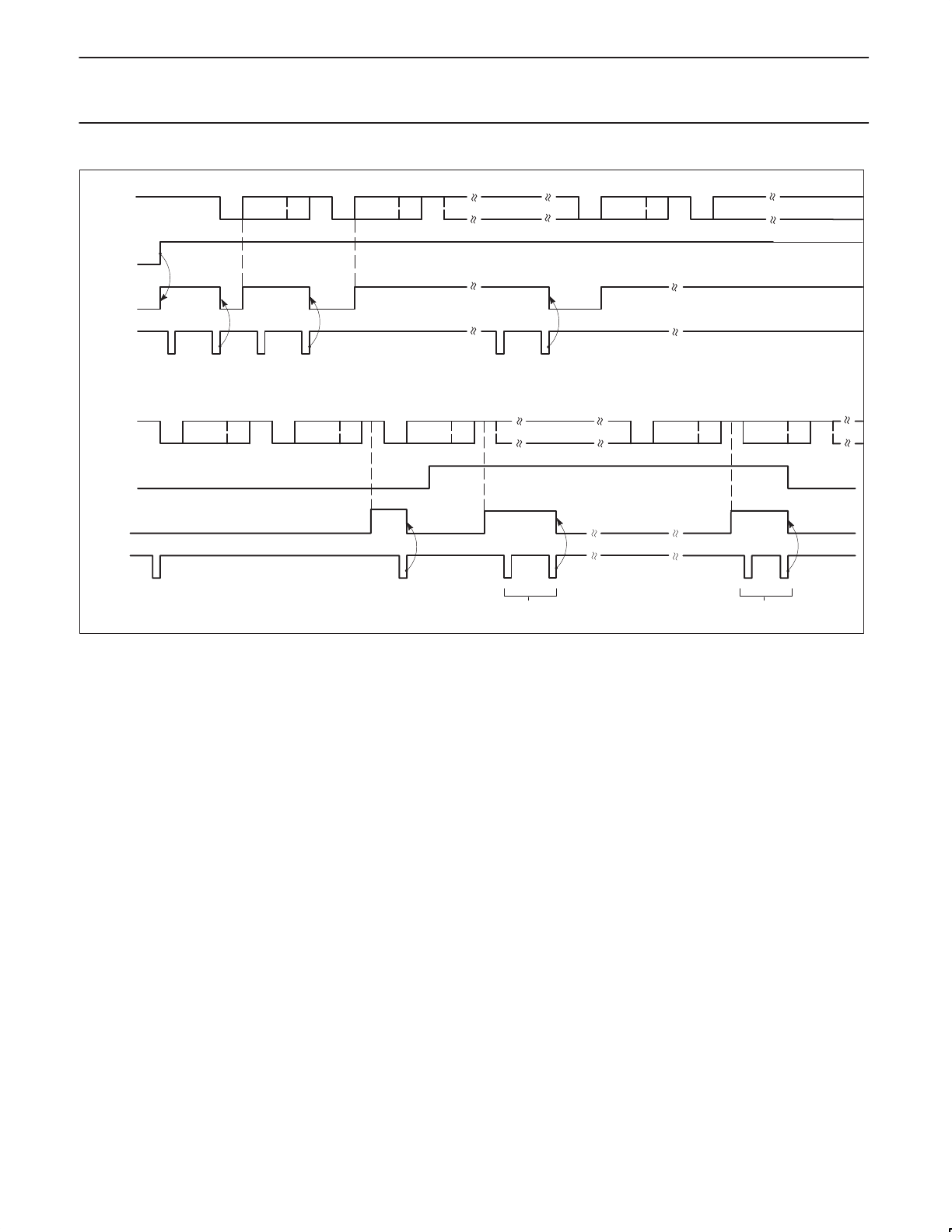

Figure 12. Wake-Up Mode

The CTS, RTS, CTS Enable Tx signals

CTS (Clear To Send) is usually meant to be a signal to the

transmitter meaning that it may transmit data to the receiver. The

CTS input is on pin MPI. The CTS signal is active low; thus, it is

called CTSN.

RTS is usually meant to be a signal from the receiver indicating that

the receiver is ready to receive data. It is also active low and is,

thus, called RTSN. RTSN is on pin MP0. A receiver’s RTS output

will usually be connected to the CTS input of the associated

transmitter. Therefore, one could say that RTS and CTS are

different ends of the same wire!

MR2(4) is the bit that allows the transmitter to be controlled by the

CTS pin (MPI). When this bit is set to one AND the CTS input is

driven high, the transmitter will stop sending data at the end of the

present character being serialized. It is usually the RTS output of

the receiver that will be connected to the transmitter’s CTS input.

The receiver will set RTS high when the receiver FIFO is full AND

the start bit of the fourth character is sensed. Transmission then

stops with four valid characters in the receiver. When MR2(4) is set

to one, CTSN must be at zero for the transmitter to operate. If

MR2(4) is set to zero, the MP pin will have no effect on the operation

of the transmitter.

MR1(7) is the bit that allows the receiver to control MP0. When MP0

is controlled by the receiver, the meaning of that pin will be RTS.

However, a point of confusion arises in that MP0 may also be

controlled by the transmitter. When the transmitter is controlling this

pin, its meaning is not RTS at all. It is, rather, that the transmitter

has finished sending its last data byte. Programming the MP0 pin to

be controlled by the receiver and the transmitter at the same time is

allowed, but would usually be incompatible.

RTS can also be controlled by the commands 1010 and 1011 in the

command register. RTS is expressed at the MP0 pin which is still an

output port. Therefore, the state of MP0 should be set low (by

commands to the CR register) for the receiver to generate the

proper RTS signal. The logic at the output is basically a NAND of

the MP0 bit register and the RTS signal as generated by the

receiver. When the RTS flow control is selected via the MR(7) bit

the state of the MP0 register is not changed. Terminating the use of

“Flow Control” (via the MR registers) will return the MP0 pin to the

control of the MP0 register.

Transmitter Disable Note

The sequence of instructions enable transmitter — load transmit

holding register — disable transmitter will result in nothing being

sent if the time between the end of loading the transmit holding

register and the disable command is less that 3/16 bit time in the

16x mode or one bit time in the 1x mode. Also, if the transmitter,

while in the enabled state and underrun condition, is immediately

disabled after a single character is loaded to the transmit holding

register, that character will not be sent.

In general, when it is desired to disable the transmitter before the

last character is sent AND the TxEMT bit is set in the status register

(TxEMT is always set if the transmitter has underrun or has just

been enabled), be sure the TxRDY bit is active immediately before

issuing the transmitter disable instruction. TxRDY sets at the end of

the “start bit” time. It is during the start bit that the data in the

transmit holding register is transferred to the transmit shift register.

Non-standard baud rates are available as shown in Table 6 below,

via the BRG Test function.