A.3 Bus Phases

Appendix A-17

After the ACK signal is false, the target may continue the transfer by driving the DB

(7-0, P) signals and asserting the REQ signal, as previously described.

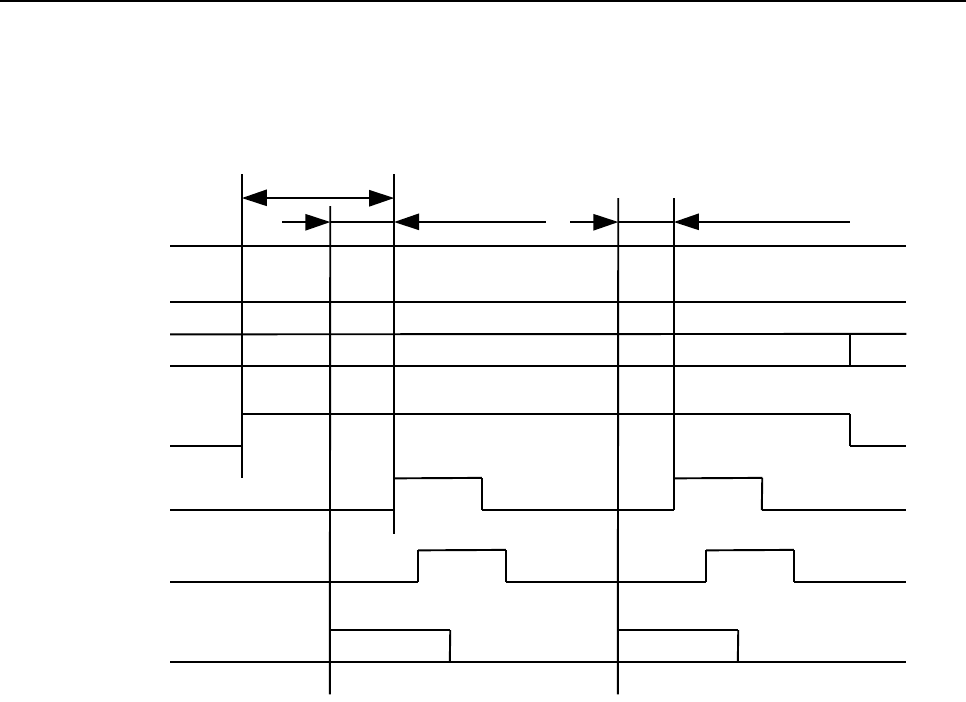

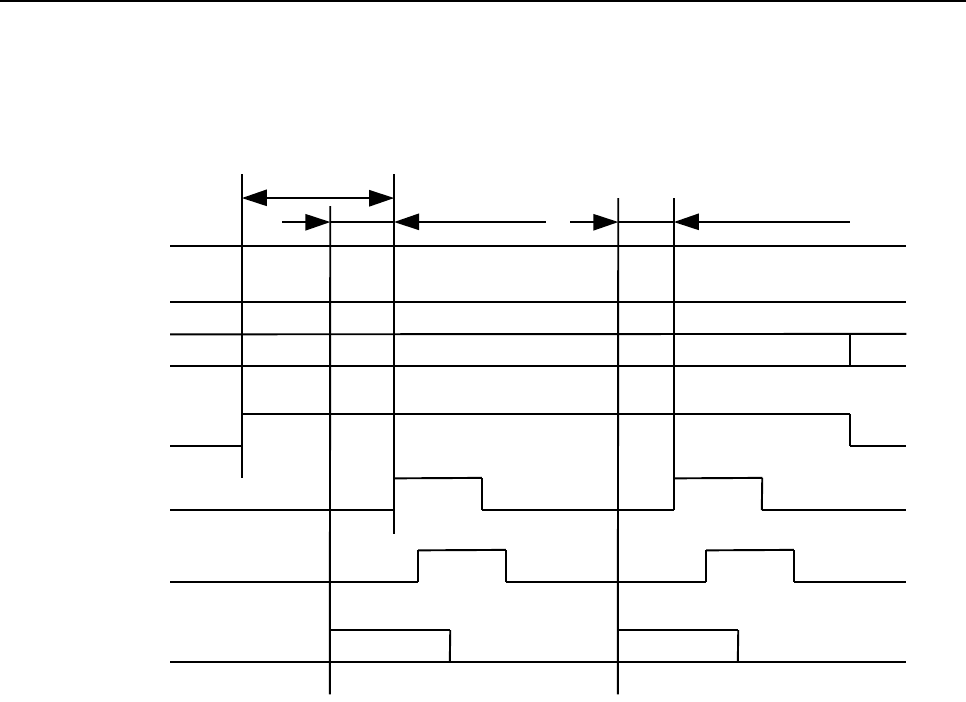

b. Asynchronous transfer from initiator to target

If the I/O signal is false (transfer to the target), the target shall request information by

asserting the REQ signal. The initiator shall drive the DB (7-0, P) signals to their

desired values, delay at least one deskew delay plus a cable skew delay then assert the

ACK signal. The initiator shall continue to drive the DB (7-0, P) signals until the REQ

signal is false. When the ACK signal becomes true at the target, the target shall read

the DB (7-0, P) signals then negate the REQ signal. When the REQ signal becomes

false at the initiator, the initiator may change or release the DB (7-0, P) signals and

shall negate the ACK signal. The target may continue the transfer by asserting the

REQ signal, as previously described.

deskew delay +

cable skew

deskew delay

+ cable skew

bus settle delay

BSY

SEL

C/D, MSG

REQ

ACK

DB

I/O