Circuit Descriptions and List of Abbreviations

EN 69DVD763SA 9.

• The Interface/Program Memory

The Loader Interface

The TZA1033HL/K2 (or DVDALAS2plus, item 7105) is an

analogue pre-processor and laser supply circuit. It contains

data amplifiers and several options for radial tracking and focus

control.

It is possible to optimise the dynamic range of this pre-amp/

processor combination for the LF servo and RF data paths. The

gain in both channels is separately programmable. This will

guarantee an optimal playability for all kind of discs.

Also, a dual laser supply is implemented, with fully automatic

laser control including stabilisation and an ON/OFF switch, plus

a separate supply pin for power efficiency.

The Servo Processor/Decoder

In the SD3.0 module, the servo signals were fed to the MACE2

servo processor, while the HF output signal was fed to the

SAA7335 decoder. In the new SD4.0SA_CH module, these ICs

are combined into one chip: the SAA7812 Iguana.

This chip contains the following blocks: channel decoder, block

decoder, servo processor, and microcontroller.

The servo circuit in the SAA7812 (item 7207) takes care of the

servo controls.

In a CD system, there are some twelve control loops active.

About six of them are needed to adjust the servo error signals

that is once per disc rotation. It also adjusts offsets, signal

amplitudes, and loop gains (AGCs), to enlarge system

robustness and to avoid expensive potentiometer adjustments

in production.

The other six loops determine the laser spot position on the

disc in the radial, axial (focus), and tangential directions.

It also has to take care that the spot accesses a required

position as fast as possible. This access system consists of two

parts, namely the actuator and the sled, which are (within a

certain range) mechanically and electrically independent.

Therefore, during an access, the servo has to control as well

the actuator as the sled.

The analogue signals, from the diode pre-processor, are

converted into a digital representation using A/D converters.

For the communication between the host processor (STi55xx)

and the servo processor, the S2B bus is used. This bus

supports full-duplex asynchronous communication.

The SAA7812 is also a combined CD/DVD compatible

decoding device. The device operates with built in hardware for

CD/DVD error correction and de-interleaving operations. It

decodes EFM or EFM+HF signals directly from the laser pre-

amplifier, including analogue front-end, PLL data recovery,

demodulation, and error correction.

Its analogue front-end input (the channel decoder), converts

the HF input signal to the digital domain via an 8-bit ADC,

preceded by an AGC circuit to obtain the optimum performance

from the converter. An external resonator clocks this block.

This subsystem recovers the data from the channel stream. It

corrects asymmetry, performs noise filtering and equalisation,

and finally recovers the bit clock and data from the channel

using a digital PLL.

The demodulator part detects the frame synchronisation

signals and decodes the EFM (14 bit) and EFM+ (16 bit) data

and sub-code words into 8-bit symbols. Via the serial output

interface, the I

2

S data (audio and video) go to the DVD decoder

STi55xx.

The spindle-motor interface provides both motor control signals

from the demodulator and, in addition, contains a tachometer

loop that accepts tachometer pulses from the motor unit. They

drive the motor IC (BA6665FM, item 7300).

The SAA7812 has two independent microcontroller interfaces.

The first is a serial I

2

C-bus and the second is a standard 8-bit

multiplexed parallel interface. Both of these interfaces provide

access to 32 8-bit registers for control and status.

The Interface/Program Memory

The interface between front-end (SAA7812) and back-end

(Sti55xx) is via:

• I2S bus (BCLK, DATA, WCLK, FLAG, SYNC and V4).

• S2B bus (RXD_S2B, TXD_S2B, CPR_S2B and

SUR_S2B).

• Miscellaneous I/O ports (RSTNF= front-end reset, EANF=

front-end processor boot select).

Service tip: These lines contain series resistors (47 or 100 Ω)

for easy hardware debugging, and for EMC/noise reduction of

the high-speed I2S lines.

The front-end processor SAA7812 (Iguana) has two boot

modes: normal boot from flash memory, or serial mode.

The boot selection is via the EANF pin. The Iguana samples the

EANF signal level once during boot-up. Once boot-up is

completed, this pin is no longer used for this purpose.

However, in the SD4.0SA_CH circuit, the EANF is also

connected to the flash memory. Therefore, when this pin is

LOW, the lower 1Mbits of the memory is accessible.

Conversely, when this pin is HIGH, the upper 1Mbits is

accessible.

Under front-end normal operation, the program memory (less

than 1Mbits in size) should reside in the lower bank. Therefore,

the EANF pin should be LOW at all times. Since the actual flash

memory used is 2Mbits, the upper 1Mbits is unused. This area

is reserved for possible use by the front-end self-diagnostic

software, or flash download application.

9.3.3 Back-end: the Digital Part

The back-end consists of:

• DVD back-end processor

• SACD DSD processor

• Audio output

• Video output

• Clock factory

• Miscellaneous

DVD Back-end Processor

The SD4.0SA_CH is designed for the Sti55xx family. Some of

the DVD related features of these ICs are:

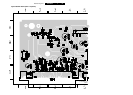

Figure 9-4 Processor overview

The STi5580 has the same architecture as the STi5508 (used

in earlier DVD generations), and is pin-to-pin compatible.

It works on 3.3 V (VDD), and comprises the following functions:

• Video decoder, which supports MPEG1 and MPEG2.

• Audio decoder that supports AC-3, MPEG1, MPEG2, DTS,

PCM, S/PDIF, and MP3.

• PAL/NTSC video encoder with simultaneously Y/C, CVBS,

and RGB/YUV outputs.

• The video encoder supports Closed Caption and allows

MacroVision 7.0/6.1.

• Full screen On Screen Display (OSD) generator.

• Three on-chip PLLs to generate all necessary clocks (as

reference the 27 MHz video clock is used).

Input

Input data comes from the I2S-bus. The front-end interface of

this device, accepts DVD, CD and CD-DA information.

Processor overview

Function STi5580 STi5588 STi5519

Basic CD/VCD/DVD decoding X X X

Extra 2-channel of I2S output (PCMDATA3) X X

Karaoke X X

DTS XX

Audio post processing (equalizer, level meter, etc) X

DVD audio X

Progressive scan at analog video output X

CL 16532163_048.eps

240102