Circuit Descriptions and List of Abbreviations

EN 70 DVD763SA9.

Signal Processing

For video, the input data stream is decoded to the appropriate

MPEG, Sub Picture, and OSD data streams, after which they

are fed to the PAL/NTSC encoder. This cell will convert the

digital MPEG/Sub Picture/OSD stream into a standard base

band signal and into RGB components. It handles interlaced

and non-interlaced data, can perform CC/TXT encoding, and

allows MacroVision copy protection.

For audio, the processing cell is a fully compatible DTS, Dolby

Digital (AC-3), MPEG1, MPEG2, PCM decoder, capable of

decoding 5.1 and 2 channel streams.

Output

For video, six analogue output pins are available on which

CVBS, S-VHS (Y/C), and RGB signals are present. They go,

via a buffer, to connector 1703. As an option, a digital YUV

output is available at connector 1704.

External Memory

The STi55xx family is capable of accessing external memory

via three buses:

• The enhanced memory interface (EMI). This interface is

configurable and can be used to access Flash, ROM, and

various flavours of DRAM.

• The shared memory interface (SMI). The SMI is only

used to access SDRAM. The SMI is connected to a

64Mbits (4M x 16bit) 7.5ns SDRAM (item 7500). The

SDRAM has the following functions:

– It is used by the MPEG video decoder as a frame

buffer,

– It holds the software and the variables used by it.

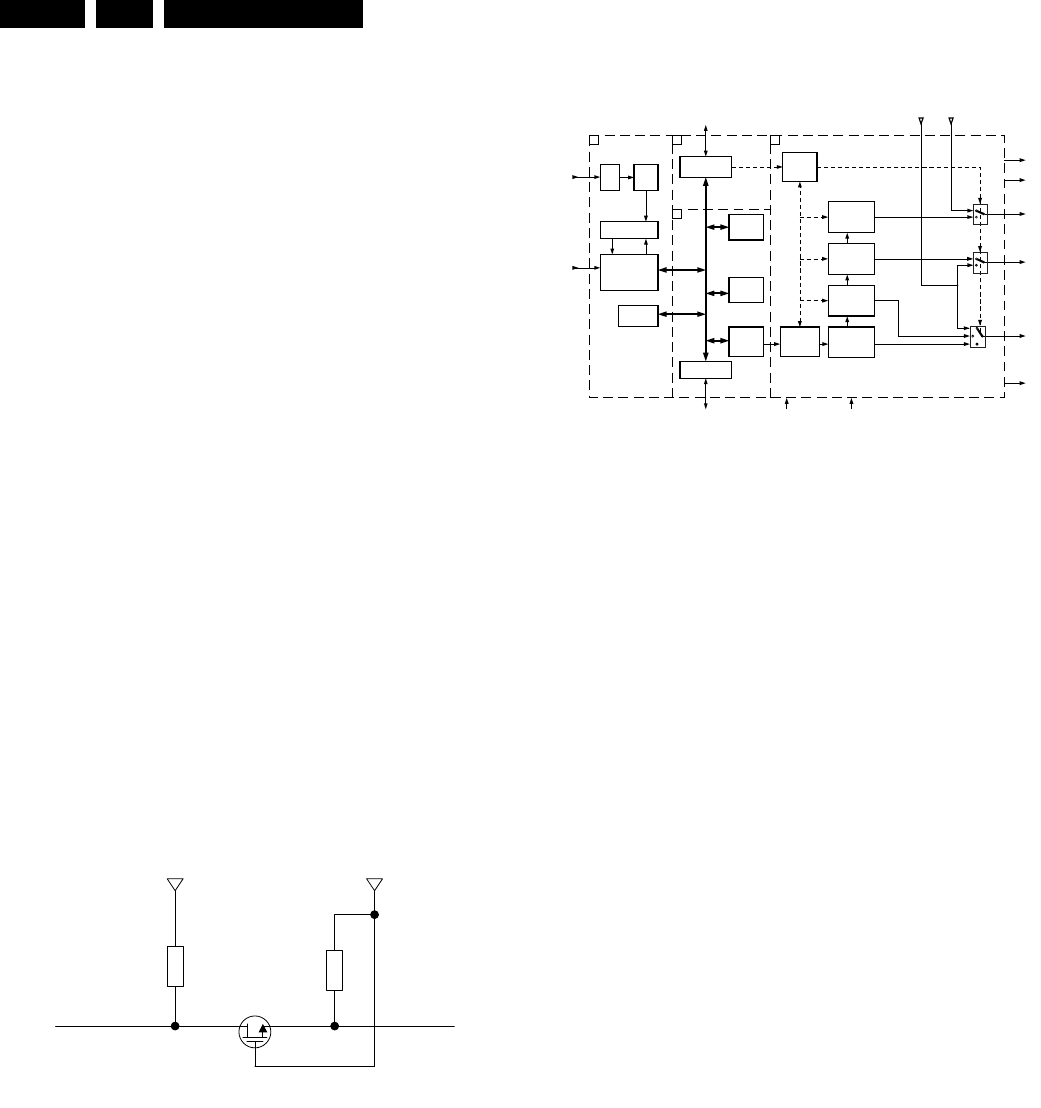

• The I2C bus. Via this bus, the NVRAM (or EEPROM) is

accessible. This memory is used to store user settings,

player settings, and region code. As the STi55xx I/O-lines

are potentially unable handle 5V inputs, a voltage level

shifter is foreseen for all I2C-busses. This circuit will isolate

the STi55xx I2C ports (3.3V) from the system I2C bus (5V).

See figure below.

Figure 9-5 I2C voltage level shifter

The SACD DSD processor

The Furore-IC is a one-chip design, containing all the hardware

that is required for SACD processing. It is intended to interface

with the STixx-family DVD video decoders.

The Furore-IC contains a memory interface to support an

external 16 or 64 Mbit SDRAM.

During SACD application, the STi55xx serves as a host,

whereby the Furore is controlled via the EMI interface. The

Furore processing part is not used during all other play modes.

In these modes, the PCM audio signals are fed through the

Furore to the appropriate DAC.

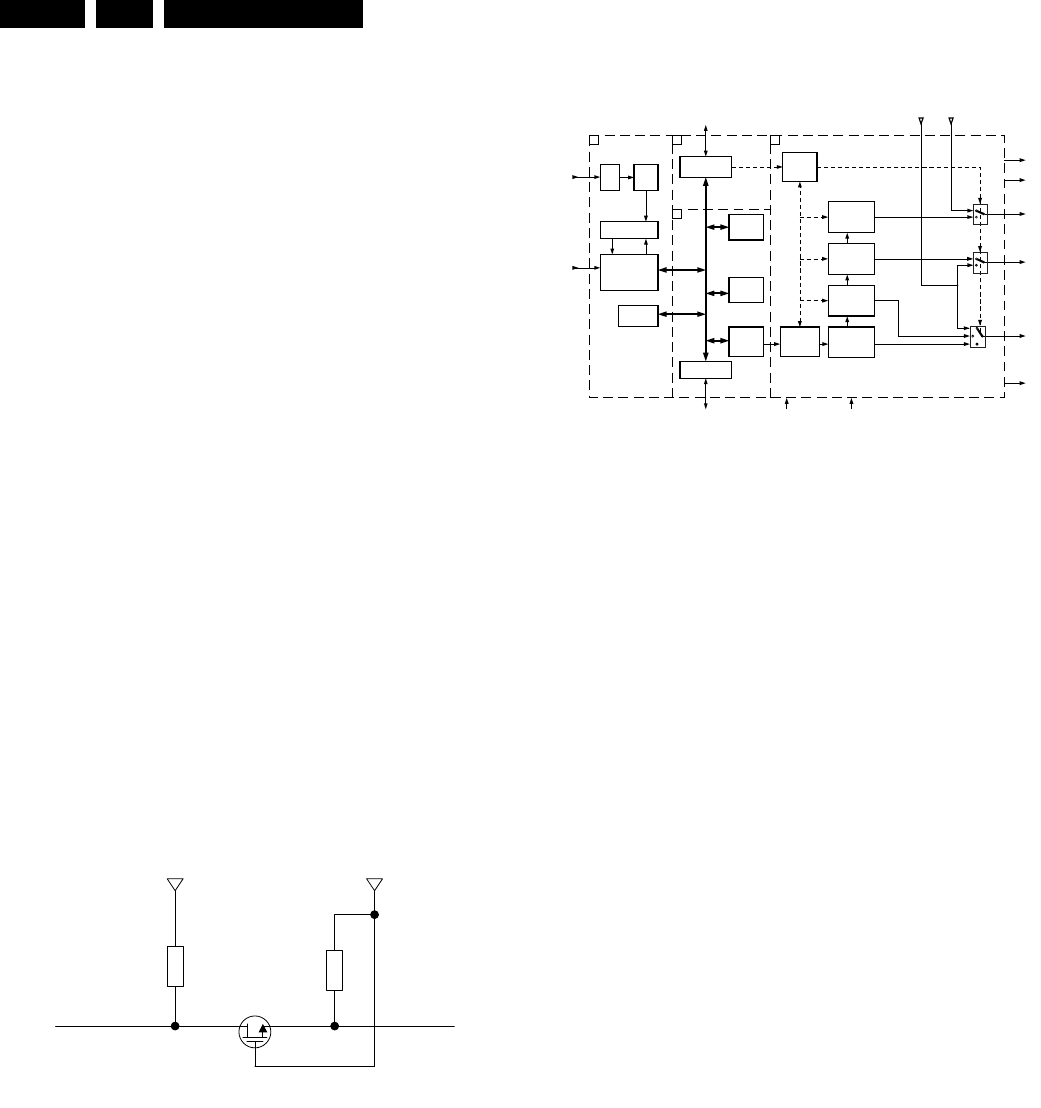

Block diagram

Figure 9-6 Block diagram Furore

We can divide the Furore-IC in four main parts (see block

diagram):

1. Host interface. This is the link between the host bus and

the internal registers and memory bus. It also supplies the

general reset signal (HW and SW) and the interrupt

signals.

2. Data processing. All modules and peripherals in this part

are connected to a so-called PI-bus. It is beyond the scope

of this manual to go more in detail on this subject.

3. Copy protection. On every SACD disc, a PSP-signal is

recorded. The player can only play a disc if a valid PSP-

signal is detected. This PSP-key is recorded, via a special

mechanism, in the EFM-signal on the disc. To detect this

key, the analogue HF-signal from the optical pick-up unit is

fed directly to the Furore-IC. Via an AGC, the signal is fed

to an ADC. The digitised HF signal is then fed to a block

where key is encrypted. Control of this process is done via

the host interface (sector processor).

4. DSD decoding and post processing. In this part, all

processing is done to generate a DSD and/or an I

2

S stream

(from the de-multiplexed stream coming from the data

processing block), in such a way that it can directly be

connected to a DA-converter. All processing is done on

384*FS.

Interfaces

• Basic Engine Interface:

– Data input interface. The Basic Engine Interface (I2S)

is connected to the output of the SAA7335 (HD61) high

speed CD decoder.

– Analogue HF input. The analogue HF input, coming

from the optical pickup unit (OPU), is also fed to the

Furore-IC, to extract the copy-protection information

PSP (Pit Signal Processing = invisible data is stored on

to disc, which is required to decrypt the encrypted

content).

• SDRAM Interface: The SDRAM interface forms a glue

less interface to one 64 Mbit SDRAM device. The interface

takes care for the power-up sequence, mode programming

and refreshing of the SDRAM devices. This is hard coded

in the interface and does not have to be controlled by the

host.

• Audio data input/output Interface:

– DSD/PCM combined data output. DSD_PCM: Output

intended for a combined 6-channel DSD (SACD) and

PCM (DVD-CDDA) DAC. Switching between the PCM

data coming from the STi55xx, and the internal

generated DSD signals, is done in the Furore IC.

– Stereo DSD only output. DSD_stereo: 2-channel DSD

output with stereo down mix in the case of 5- and 6-

channel, and normal stereo in case of 2-channel DSD

mode.

3V3

3k3

5V

3k3

(optional)

5V I2C levels 3.3V I2C levels

CL 16532163_050.eps

230102

Decryption

/

Sector

Processor

AGC

8 bits

AD

PSP-key

decoder

Key

Host interface

Demux

SDRAM

interface

SACD

Audio

interface

PI-Bus

Control

2 -5 -6 ch

LossLess

decoder

6 channel

fade

To Host processor

(STi 55XX)

From Host processor

(STi 55XX)

to 16 Mbit/64 Mbit

SDRAM

PCM_CLK

PI-bus

Control

Register

Host

interface

DSD

mix

IEC 958

gen.

DSD -->PCM

(stereo)

AUD_CLK

256/384/512/718

*

FS

FS = 44.1 - 48 KHz

PCM

I

2

S

I

2

S

HF

Memory

manager

SYS_CLK

27-35 MHz

CL 26532053_021.eps

260402

(BE Interface)

3 41

2

DSD_CLK

IEC 958

PCM

DSD/PCM

MUTE

IEC 958