FX Series Programmable Controllers PLC Device Tables 8

8-9

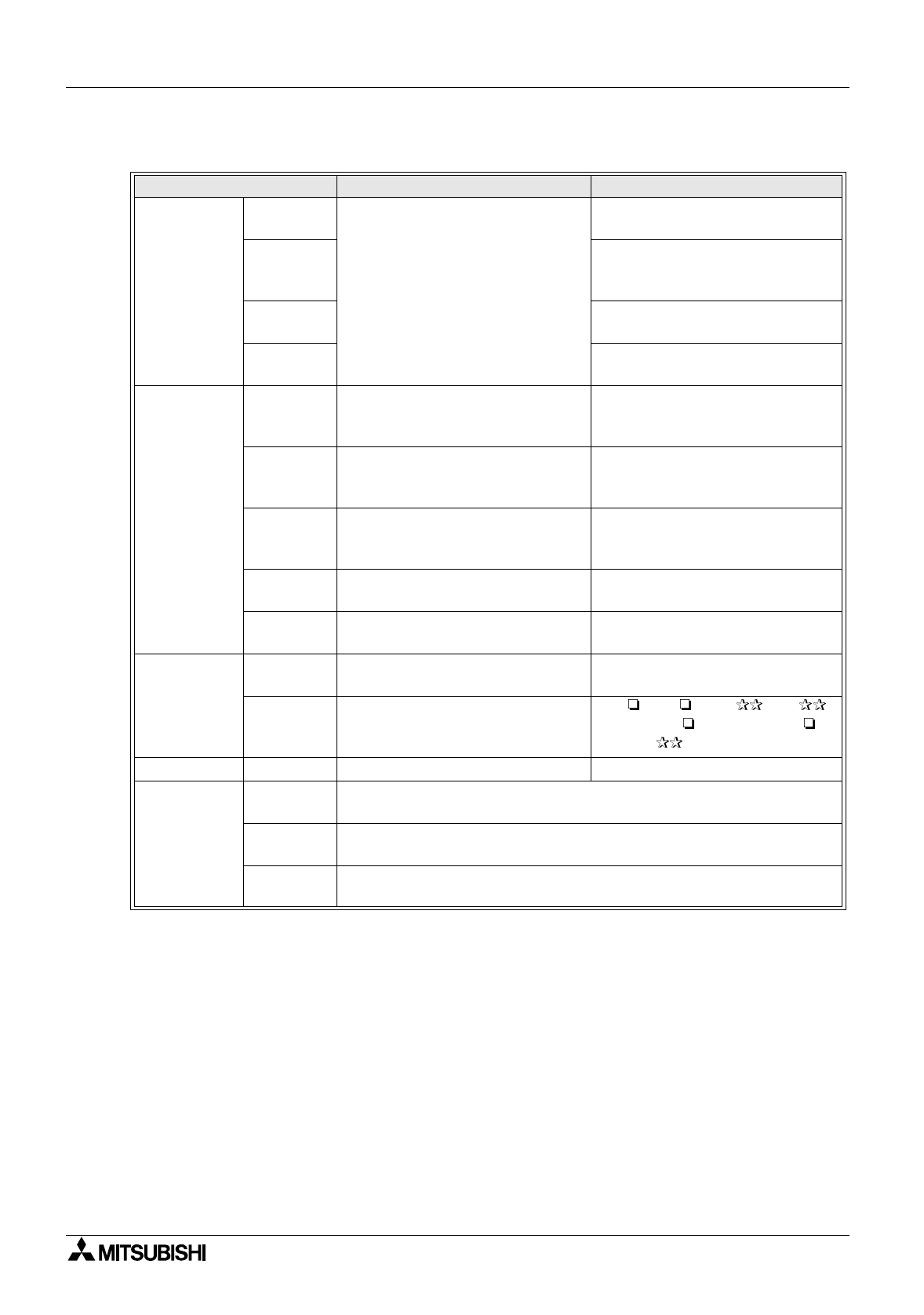

Item Specification Remarks

Hi

g

h speed

counters (C)

1 phase

Ran

g

e: -2,147,483,648 to

+2,147,483,647 counts

General rule: Select counter com-

binations with a combined countin

g

frequenc

y

of 20kHz or less.

Note all counters are latched

C235 to C240

6 points

1 phase

c/w start

stop input

C241 to C245

5 points

2 phase

C246 to C250

5 points

A/B phase

C251 to C255

5 points

Data

re

g

isters (D)

General 8000 points

D0 to D7999

T

y

pe: 16 bit data stora

g

e re

g

ister

pair for 32 bit device

Latched 7800 points (subset)

D200 to D7999

T

y

pe: 16 bit data stora

g

e re

g

ister

pair for 32 bit device

File

re

g

isters

7000 points

D1000 to D7999 set b

y

parameter

in 14 blocks of 500 pro

g

ram steps

T

y

pe: 16 bit data stora

g

e re

g

ister

Special 256 points

From the ran

g

e D8000 to D8255

T

y

pe: 16 bit data stora

g

e re

g

ister

Index 16 points

V0 to V7 and Z0 to Z7

T

y

pe: 16 bit data stora

g

e re

g

ister

Pointers (P)

For use

with CALL

128 points P0 to P127

For use

with

interrupts

6 input points, 3 timers, 6 counters

I00 to I50 and I6 to I8

(risin

g

tri

gg

er =1, fallin

g

tri

gg

er =0,

=time in msec)

Nest levels 8 points for use with MC and MCR N0 to N7

Numbers

Decimal K

16 bit: -32,768 to +32,767

32 bit: -2,147,483,648 to +2,147,483,647

Hexadeci-

mal H

16 bit: 0000 to FFFF

32 bit: 00000000 to FFFFFFFF

Floatin

g

Point

32 bit: 0, ±1.175 x 10

-38

, ±3.403 x 10

38

(Not directl

y

enterable)