Functional Description

20

SLES140A—March 2007TVP5147M1PFP

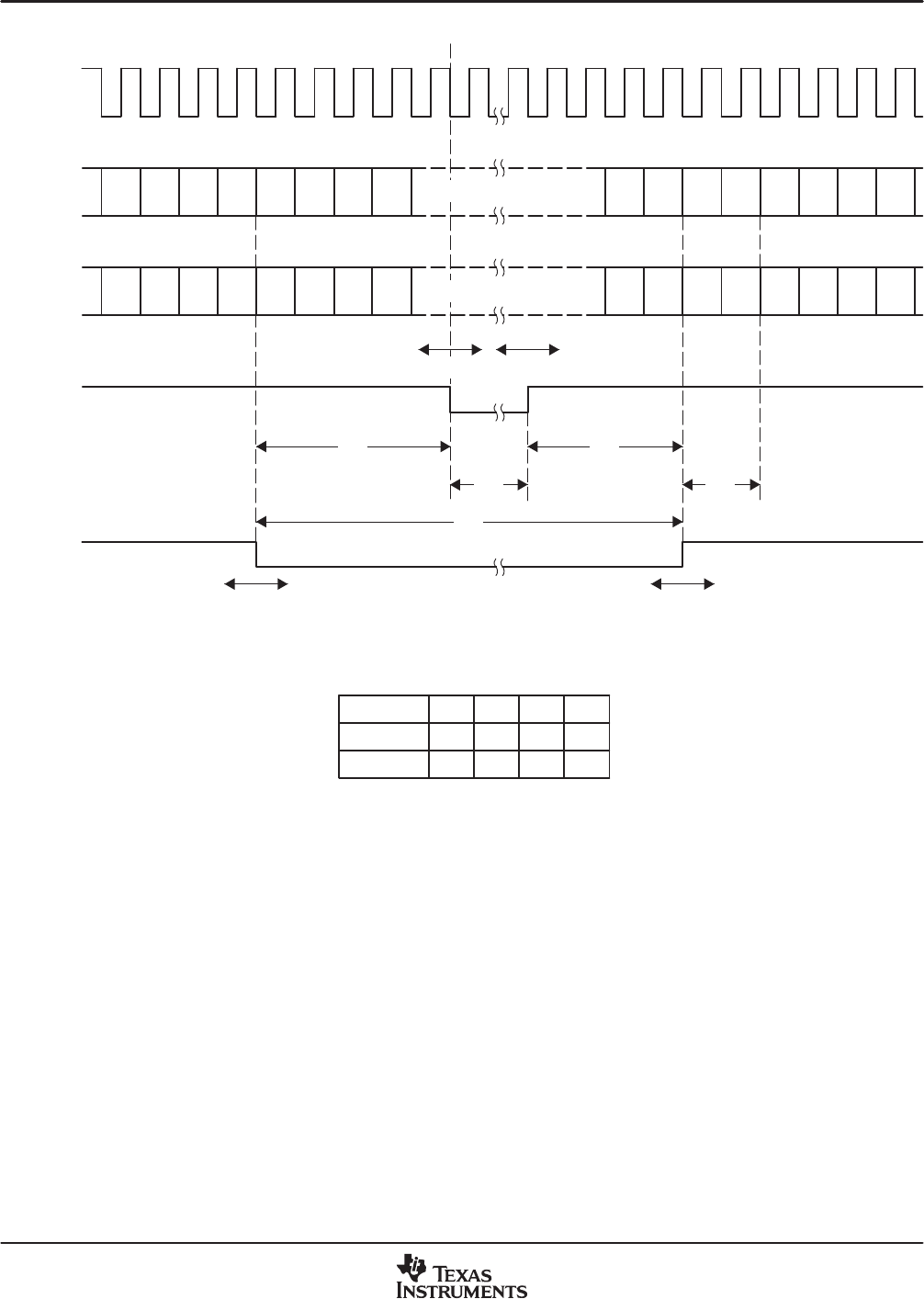

CbCr[9:0]

NTSC 601 53

PAL 601

DATACLK = 1× Pixel Clock

56

64

64

19

22

Mode A BC

136

142

D

Cb

D

ATACLK

Cr Cb Cr Cb0 Cr0 Cb1 Cr1

0

HS Start

Horizontal Blanking

HS

HS Stop

A C

B

AVID

D

NOTE: AVID rising edge occurs 4 clock cycles early.

Y[9:0] Y Y Y Y Y0 Y1 Y2 Y3Horizontal Blanking

2

AVID Stop AVID Start

NOTE: 20-bit 4:2:2 timing with 1× pixel clock reference

Figure 2−15. Horizontal Synchronization Signals for 20-Bit 4:2:2 Mode