Electrical Specifications

81

SLES140A—March 2007 TVP5147M1PFP

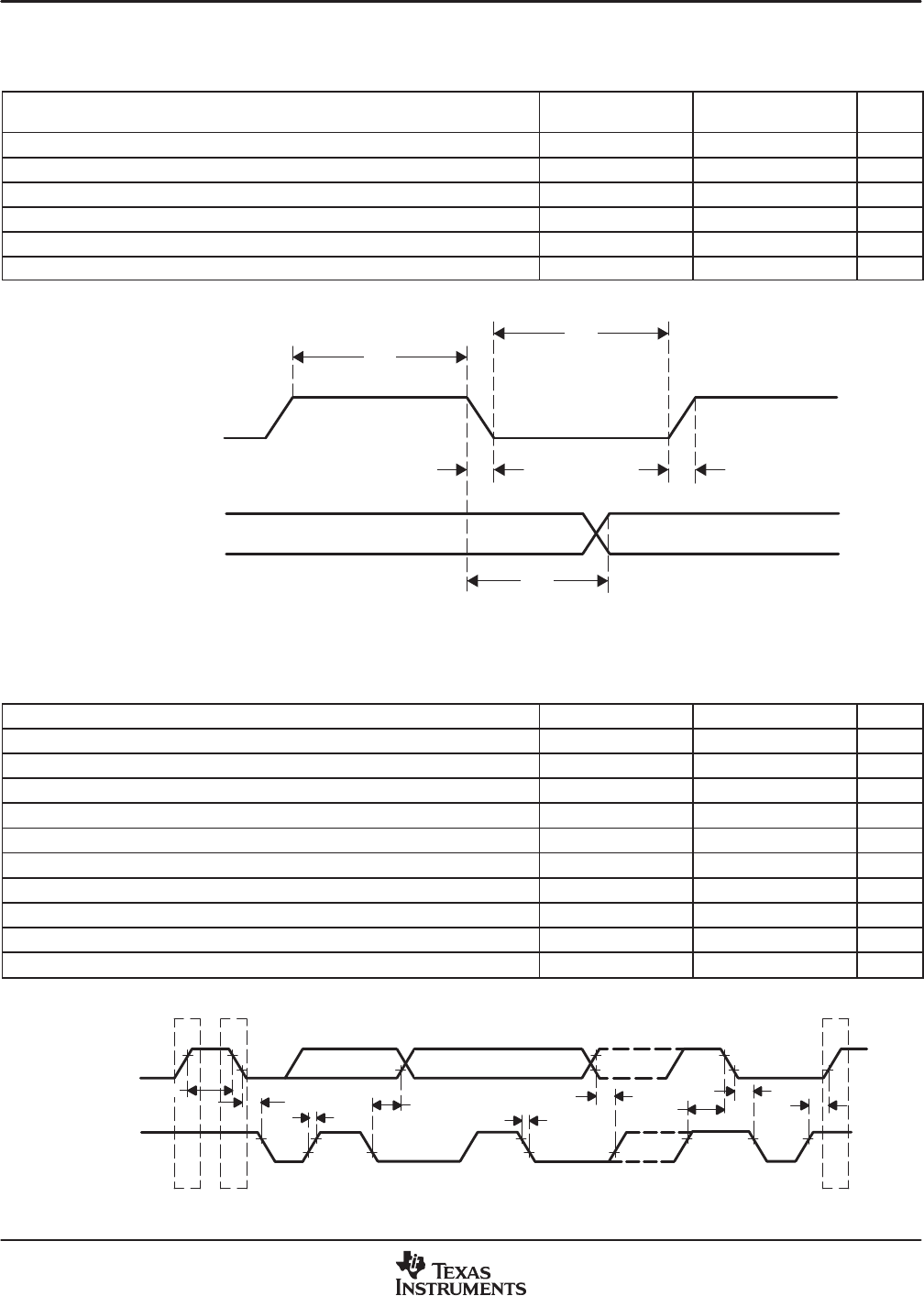

3.3.3 Timing

3.3.3.1 Clocks, Video Data, Sync Timing

PARAMETER

TEST CONDITIONS

(see NOTE 1)

MIN TYP MAX UNIT

Duty cycle DATACLK 45% 50% 55%

t

1

High time, DATACLK 18.5 ns

t

2

Low time, DATACLK 18.5 ns

t

3

Fall time, DATACLK 90% to 10% 4 ns

t

4

Rise time, DATACLK 10% to 90% 4 ns

t

5

Output delay time 10 ns

NOTE 1: C

L

= 15 pF

t

1

DATACLK

Y, C, AVID, VS, HS, FID

t

4

t

2

t

3

t

5

V

OH

V

OL

Valid Data Valid Data

V

OH

V

OL

Figure 3−1. Clocks, Video Data, and Sync Timing

3.3.3.2 I

2

C Host Port Timing

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

t

1

Bus free time between STOP and START 1.3 µs

t

2

Data hold time 0 0.9 µs

t

3

Data setup time 100 ns

t

4

Setup time for a (repeated) START condition 0.6 µs

t

5

Setup time for a STOP condition 0.6 ns

t

6

Hold time for a (repeated) START condition 0.6 µs

t

7

Rise time VC1(SDA) and VC0(SCL) signal 250 ns

t

8

Fall time VC1(SDA) and VC0(SCL) signal 250 ns

C

b

Capacitive load for each bus line 400 pF

f

I2C

I

2

C clock frequency 400 kHz

t

5

Stop Start

VC1 (SDA)

t

1

t

6

t

7

t

2

t

8

t

3

t

4

t

6

VC0 (SCL)

Data

Stop

Change

Data

Figure 3−2. I

2

C Host Port Timing