Circuit Descriptions and List of Abbreviations

EN 90 DVD963SA9.

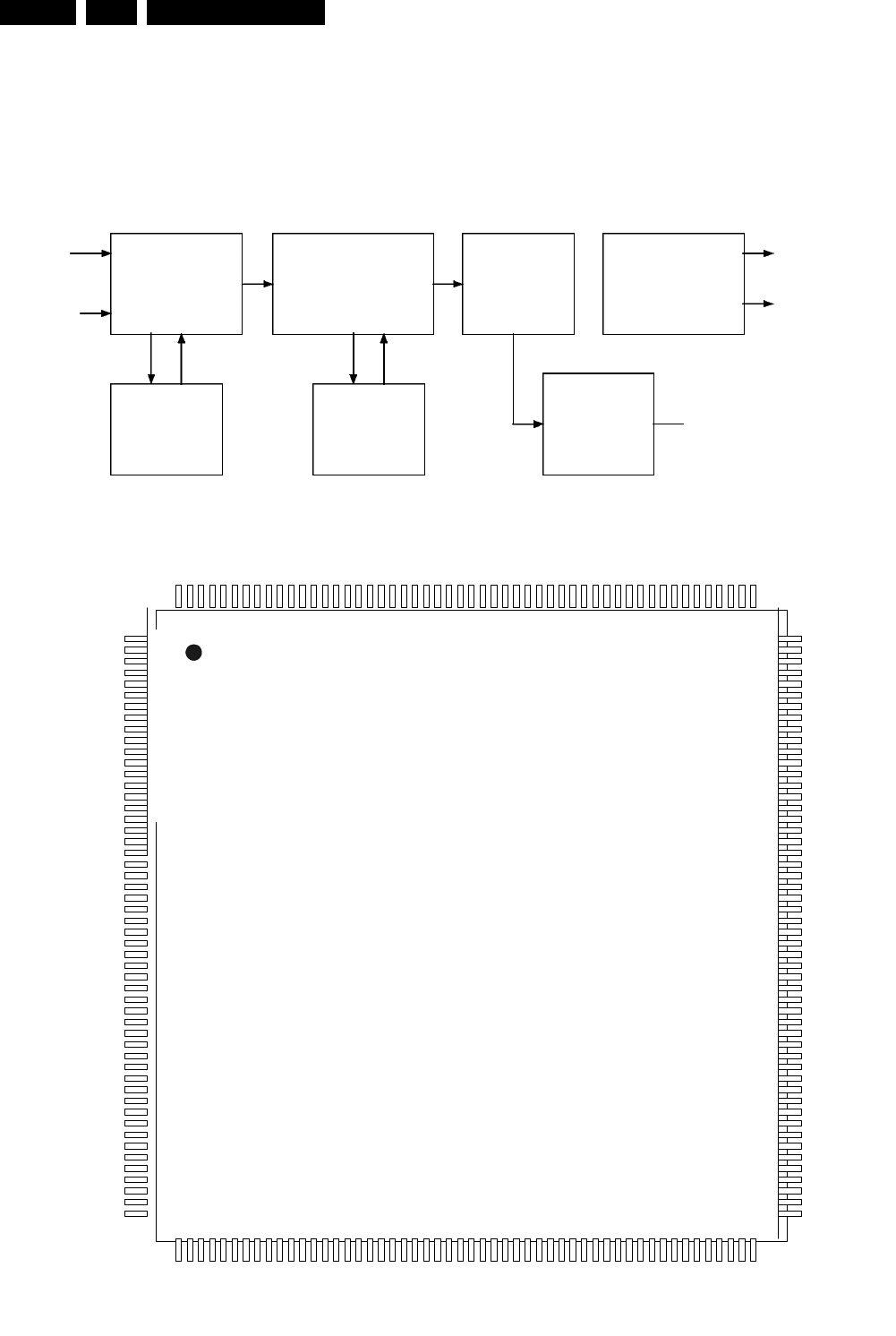

9.9.4 Diagram P1: FLI2301 (item 7100)

Figure 9-18 FLI2301 (item 7100)

BLOCKDIAGRAM

ñ

Simplified Internal Block Diagram

Input Processor

with Auto Sync

and auto Adjust

Noise Reducer,

Deinterlacer, Frame

Rate Converter and

SDRAM interface

Port 2

8-bit

656 Input

Port 1

8/16/24-bit

RGB/YCrCb

Input

Clock

Generation

PLLs

2Mx32

SDRAM

(external)

Vertical and

Horizontal

Scalers

Vertical and

Horizontal

Enhancers

Output

Processor with

Sync Generation

and DACs

16/20/24-bit

RBG/YCrCb

Digital Outputs

RBG/YCrCb

Analog Outputs

1 5 5

1 5 0

1 4 5

1 4 0

1 3 5

1 3 0

1 2 5

1 2 0

1 1 5

1 1 0

1 0 5

1

5

1 0

1 5

2 0

2 5

3 0

3 5

4 0

4 5

5 0

5 5

6 5

6 0

1 0 0

9 5

9 0

8 5

8 0

7 5

7 0

2 0 5

1 9 5

2 0 0

1 6 0

1 6 5

1 7 0

1 7 5

1 8 0

1 8 5

1 9 0

HSYNC1_PORT1

VDD1

B/Cb/D1_0

VSS

IN_CLK1_PORT1

FIELD ID1_PORT1

VSYNC1_PORT1

HSYNC2_PORT1

IN_CLK2_PORT1

FIELD ID2_PORT1

VSYNC2_PORT1

B/Cb/D1_6

B/Cb/D1_5

B/Cb/D1_4

B/Cb/D1_3

B/Cb/D1_2

B/Cb/D1_1

B/Cb/D1_7

VDDcore1

VSScore

R/Cr/Cb Cr_0

R/Cr/Cb Cr_6

R/Cr/Cb Cr_5

R/Cr/Cb Cr_4

R/Cr/Cb Cr_3

R/Cr/Cb Cr_2

R/Cr/Cb Cr_1

R/Cr/Cb Cr_7

VDD2

VSS

G/Y/Y_0

G/Y/Y_1

G/Y/Y_6

G/Y/Y_5

G/Y/Y_4

G/Y/Y_3

G/Y/Y_2

G/Y/Y_7

VDDcore2

VSScore

IN_SEL

TEST

DEV_ADDR1

DEV_ADDR0

SCLK

SDATA

RESET_N

VDD3

VSS

SDRAM DATA(0)

SDRAM DATA(2)

SDRAM DATA(1)

SDRAM DATA(3)

SDRAM DATA(10)

SDRAM DATA(9)

SDRAM DATA(8)

SDRAM DATA(7)

SDRAM DATA(6)

SDRAM DATA(5)

SDRAM DATA(4)

SDRAM DATA(17)

SDRAM DATA(16)

SDRAM DATA(15)

SDRAM DATA(14)

SDRAM DATA(12)

SDRAM DATA(13)

SDRAM DATA(11)

VDD4

VSS

VDDcore3

VSScore

SDRAM DATA(20)

SDRAM DATA(19)

SDRAM DATA(18)

SDRAM DATA(31)

SDRAM DATA(30)

SDRAM DATA(29)

SDRAM DATA(28)

SDRAM DATA(26)

SDRAM DATA(27)

SDRAM DATA(25)

SDRAM DATA(24)

SDRAM DATA(23)

SDRAM DATA(21)

SDRAM DATA(22)

VDDcore4

VSScore

VSS

VDD5

TEST IN

SDRAM ADDR(10)

SDRAM ADDR(5)

SDRAM ADDR(4)

SDRAM ADDR(3)

SDRAM ADDR(6)

SDRAM ADDR(7)

SDRAM ADDR(8)

SDRAM ADDR(9)

VDDcore5

VSScore

SDRAM ADDR(0)

SDRAM ADDR(1)

SDRAM ADDR(2)

SDRAM WEN

B/U/Pb_OUT_7

VDDcore7

VSScore

R/V/Pr_OUT_7

VDD8

VSS

G/Y/Y_OUT_7

G/Y/Y_OUT_1

G/Y/Y_OUT_2

G/Y/Y_OUT_3

G/Y/Y_OUT_4

G/Y/Y_OUT_5

G/Y/Y_OUT_6

G/Y/Y_OUT_0

R/V/Pr_OUT_0

R/V/Pr_OUT_1

R/V/Pr_OUT_2

R/V/Pr_OUT_3

R/V/Pr_OUT_4

R/V/Pr_OUT_5

R/V/Pr_OUT_6

B/U/Pb_OUT_0

B/U/Pb_OUT_1

B/U/Pb_OUT_2

B/U/Pb_OUT_3

B/U/Pb_OUT_4

B/U/Pb_OUT_5

B/U/Pb_OUT_6

VSS

VDD7

CLKOUT

VSScore

VDDcore6

TEST OUT1

CTLOUT4

CTLOUT0

CTLOUT1

CTLOUT2

CTLOUT3

TEST OUT0

TEST3

SDRAM CLKIN

SDRAM CLKOUT

VSS

VDD6

SDRAM DQM

SDRAM CASN

SDRAM BA1

SDRAM BA0

SDRAM CSN

SDRAM RASN

OE

PLL_PVDD

PLL_PVSS

AVSS_PLL_BE1

AVDD_PLL_BE1

AVSS_PLL_SDI

AVSS_PLL_FE

AVSS_PLL_BE2

AVDD_PLL_FE

AVDD_PLL_SDI

AVDD_PLL_BE2

DAC_PVSS

DAC_VDD

DAC_VSS

DAC_B_OUT

DAC_G_OUT

DAC_R_OUT

DAC_AVDDB

DAC_AVDDR

DAC_AVDDG

DAC_AVSSB

DAC_AVSSR

DAC_AVSSG

DAC_COMP

DAC_RSET

DAC_VREFOUT

DAC_VREFIN

DAC_AVDD

DAC_AVSS

DAC_GR_AVSS

DAC_GR_AVDD

DAC_PVDD

TEST0

TEST1

TEST2

XTAL IN

XTAL OUT

VDD9

VSS

HSYNC_PORT2

IN_CLK_PORT2

FIELD ID_PORT2

VSYNC_PORT2

VSScore

VDDcore8

D1_IN_0

D1_IN_7

D1_IN_6

D1_IN_5

D1_IN_4

D1_IN_3

D1_IN_2

D1_IN_1

PinDiagram

CL 26532105_056.eps

300802