www.vxitech.com

SVM2608 Programming 33

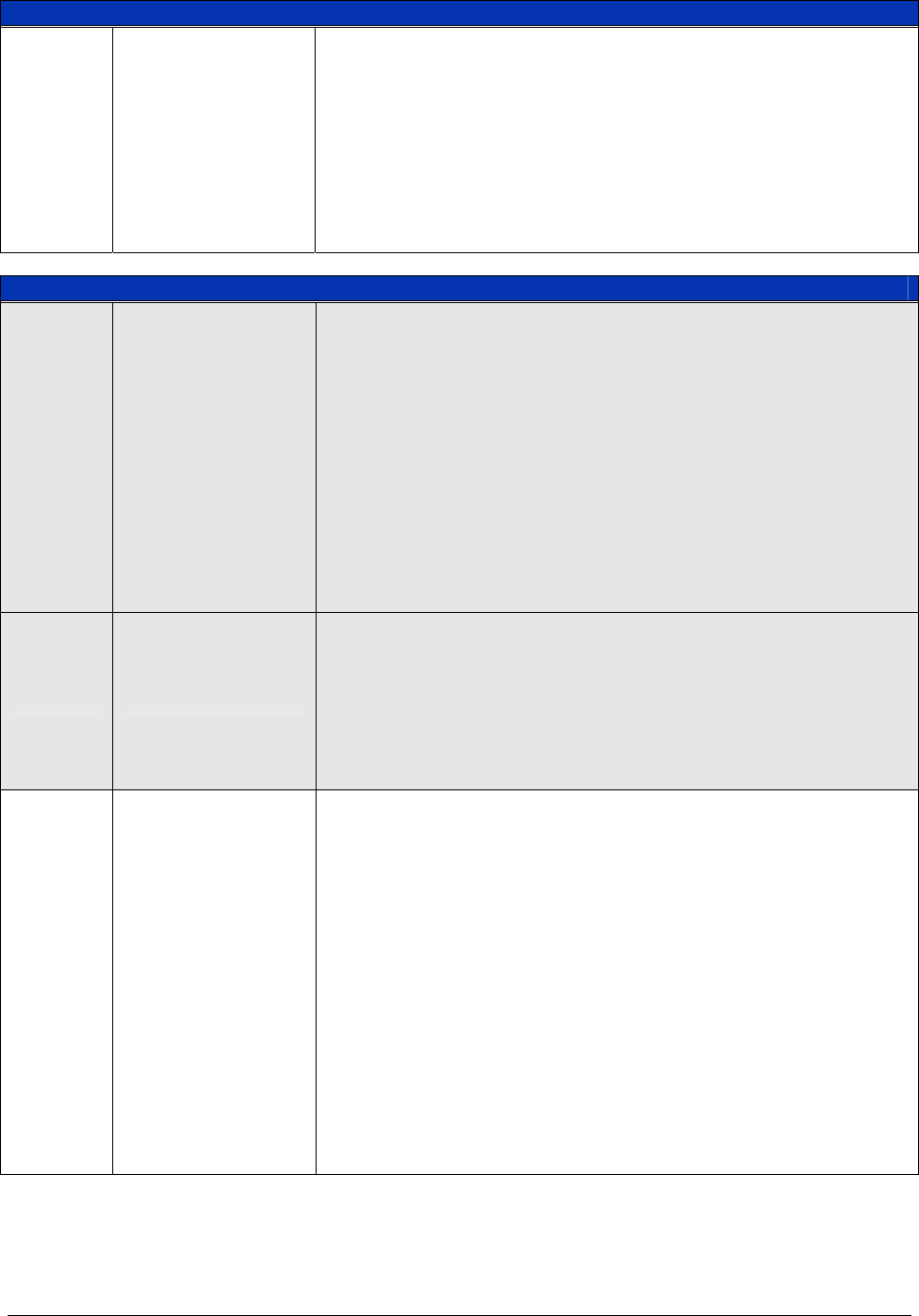

Reset, Sys Fail Control, Interrupt Levels Register (0x00) — Read & Write

D2 – D0 INTLVL2 - 0

Interrupt Level - These bits determine the interrupt service level.

111 = Interrupt level 7

110 = Interrupt level 6

101 = Interrupt level 5

100 = Interrupt level 4

011 = Interrupt level 3

010 = Interrupt level 2

001 = Interrupt level 1

000 = No interrupt

Force Trigger, Start Register (0x02) — Read & Write

D15 – D13 HS_TRIGSRC2 - 0

High-Speed Trigger Source – These bits select a trigger source for the

high-speed channels.

000 = Channel 0

001 = Channel 1

010 = Channel 2

011 = Channel 3

100 = Invalid state

101 = Invalid state

110 = External

111 = Invalid state

Note: These bits are only utilized by high-speed Channels 4 and 5. These

bits are unused for Channels 0 – 3.

D12 EXT TRIG SLOPE

External Trigger Slope – This bit sets the slope of the external trigger

for low-speed Channels 0 - 3.

0 = Positive

1 = Negative

Note: This bit is only utilized by high-speed Channels 4 and 5. This bit is

unused for Channels 0 – 3.

D11 – D6 FTRIG5 - 0

Force Trigger - All of the channels have the ability to be triggered via

software when in the arm mode. Acquisition begins when trigger is

forced. These bits need to be reset to ‘0’ in order to allow subsequent

triggers (it is the transition of a bit from 0 to 1 that forces a trigger). One

bit is assigned to each channel as follows:

D6 for Channel 0

D7 for Channel 1

D11 for Channel 5

Having one bit per channel allows multiple channels to be triggered

simultaneously.

0 = Do not force trigger

1 = Force software trigger

P

on

state =0