Overview

R

AC ’97 Programmer’s Reference Manual 15

2.1.2 Dedicated S/P DIF DMA Output Channel

The ICH5 controller provides a dedicated DMA engine with the capability of outputting either

PCM or AC-3 data to the S/P DIF link for pass-through to an external CE audio decoder. This

capability allows for simultaneous output of PCM/AC-3 on the S/P DIF link while PCM data is

output to the PCM Out DMA engine. As a result, an AC3 stream from DVD movie playback can

be output on the S/P DIF link concurrently with other system audio data (e.g., voice audio from a

telephony application).

2.1.3 20 Bits Surround PCM Output

The AC ’97 Component Specification provides a maximum bit resolution of 20 bits per sample.

The ICH5 AC ’97 controller PCM Output DMA Engine fully exploits this capability to improve

the audio output quality.

2.1.4 Memory Map Status and Control Registers

The ICH5 support PCI Memory Base Address Register that allows for higher performance access

to the controller registers while expanding the register space to access the third codec support

mechanism. All features can now be accessed via this Memory BAR making the I/O BAR

capabilities obsolete. However, the ICH5 controller may maintain the I/O BAR capability to allow

for the reuse of legacy code maintaining backward compatibility to deployed driver binaries.

Note: This document describes the programming interface using the Memory BAR registers unless

otherwise indicated. The default configuration for ICH5 Audio function is to use the PCI Memory

Base Address Register. The I/O BAR is therefore disabled unless system BIOS enables the

simultaneous backward-compatible capability on the register:

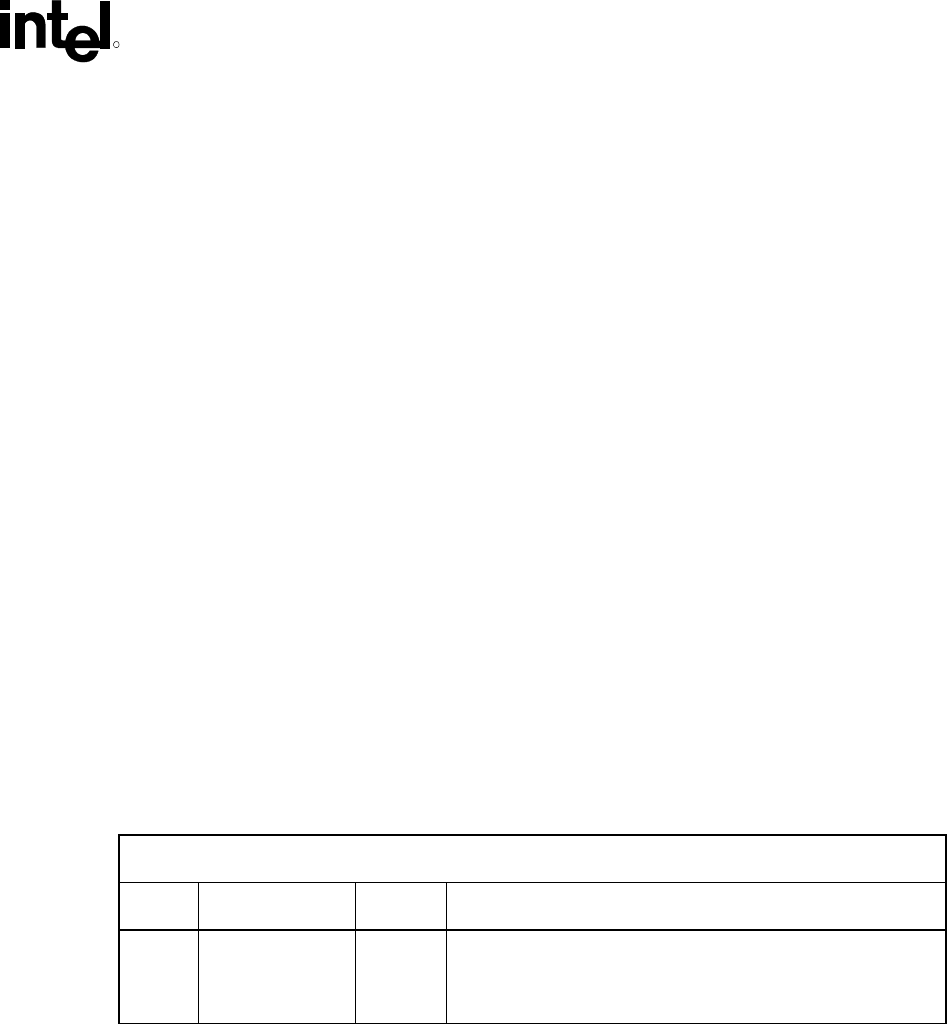

Device 31 Function 5 Audio

Offset Register Default Comments

41h CFG

Configuration

00h When cleared, the I/O space BARs at offset 10h and 14h become

read only registers. This is the default state for the I/O BARs.

Initialized by BIOS when backward I/O Bar compatibility is

required Memory BARs are always enabled.