Intel® ICH5 AC ’97 Controller Theory of Operation

R

AC ’97 Programmer’s Reference Manual 21

Table 6. BD Control and Length (DWORD 1: 04-07h)

Bit Description

31 Interrupt on Completion (IOC) 1= Enable , 0 = Disable. When this it is set, it means the

controller should issue an interrupt upon completion of this buffer. It should also set the IOC bit

in the status register.

30 Buffer Underrun Policy (BUP) 0 = When this buffer is complete, if the next buffer is not yet

ready, (last valid buffer has been processed) then continue to transmit the last valid sample.

1 = When this buffer is complete, if this is the last valid buffer, transmit zeros after this buffer is

completely processed. This bit will typically be set only if this is the last buffer in the current

stream.

29:16 Reserved. Must be 0 when writing this field.

15:0 Buffer length. This is the length of the data buffer in number of samples. The controller uses

this data to determine the length of the buffer in bytes. A value of 0 indicates no sample

to

process.

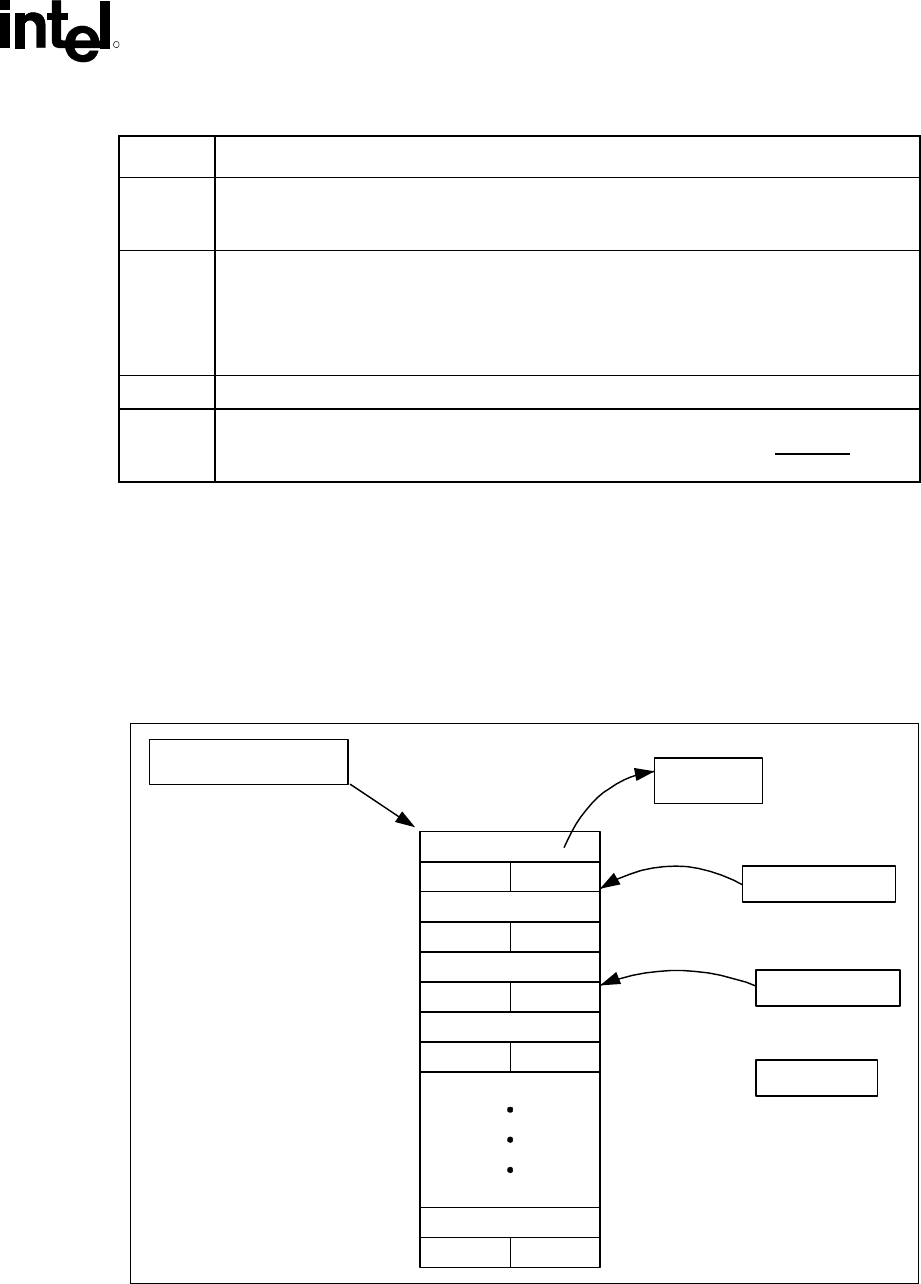

3.2.2 DMA Initialization

The maximum length of the buffer descriptor list is fixed at 32 (this is limited by the size of the

index registers). Figure 4, below, describes the organization of the Buffer Descriptor List.

Figure 4. Buffer Descriptor List

n

Buffer Descriptor List

Base Add

Data Buffer

Current Index

Prefetched Index

Last Valid

Buffer Pointer

Command Length

Buffer Pointer

Command Length

Buffer Pointer

Command Length

Buffer Pointer

Command Length

Buffer Pointer

Command Length

n-1

n+1