Intel® ICH5 AC ’97 Controller Theory of Operation

R

26 AC ’97 Programmer’s Reference Manual

3.4.3 FIFO Organization

The ICH5 AC ’97 controller supports 16-bit samples on all channels except PCM Out, which also

supports 20-bit samples.

Data will be written to the FIFO in sample pairs following the order of valid slots in a channel. For

example, for audio PCM In, the controller will check the first valid slot and add it to the FIFO first

entry as a word (16 bits). The next valid slot will be added as the second word entry in the FIFO to

create the PCM stereo sample pair. This behavior works under the assumption that the first valid

slot will be always the Left channel (slot 3) followed by Right channel in slot 4 in the same or

subsequent frame. If the codec transmits data repeating the slot, it will cause the controller to

misplace the sample in the FIFO. Codecs compatible with the ICH5 AC ’97 implementation

should always maintain the indicated order, and never use the same slot twice to transmit samples

to the controller. The figures below present some ICH5 compatible and incompatible

implementations using as a reference a two-channel implementation.

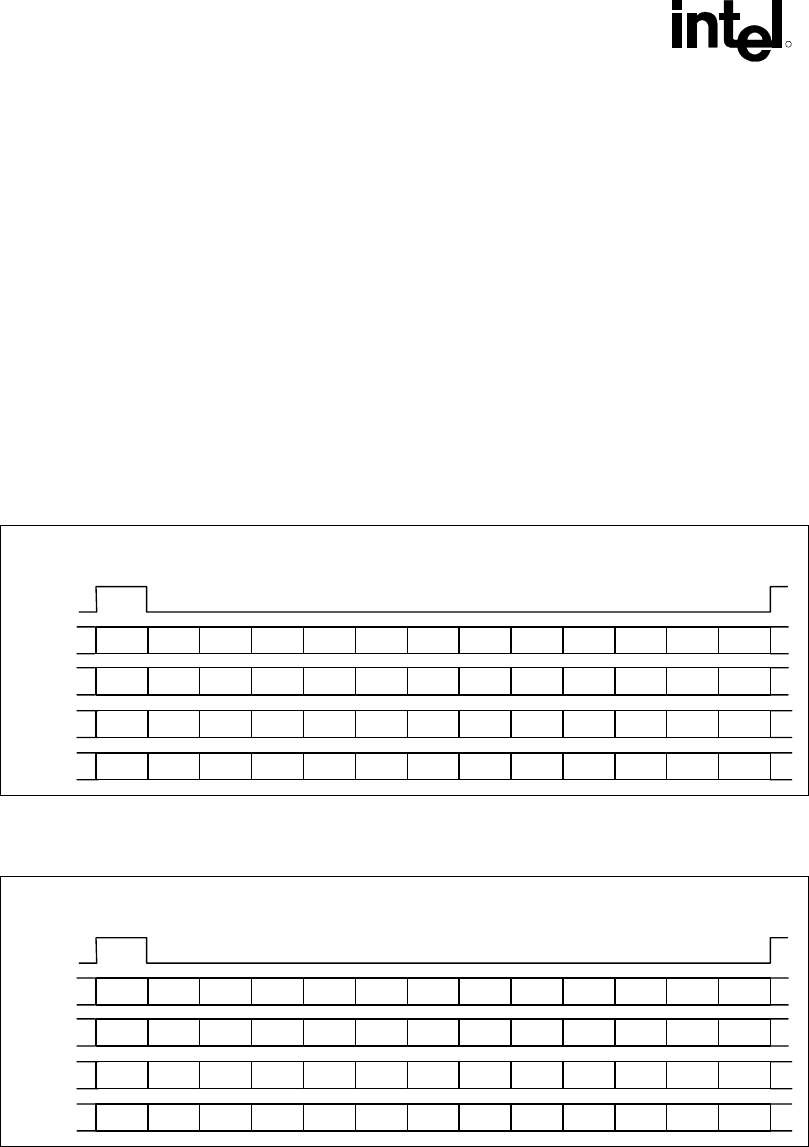

Figure 5. Compatible Implementation with Left and Right Sample Pair in Slot 3/4 Every Frame

Frame n

Frame n + 1

Frame n + 2

Frame n + 3

X

CMD

DATA

MDM

CDC

RSVD RSVD RSVD RSVD RSVD RSVD

I/O

Control

CMD

ADR

TAG X

X

CMD

DATA

MDM

CDC

MIC RSVD RSVD RSVD RSVD RSVD

I/O

Status

Status

Data

Status

ADR

TAG X

X

CMD

DATA

MDM

CDC

RSVD RSVD RSVD RSVD RSVD RSVD

I/O

Control

CMD

Data

CMD

ADR

TAG X

X

CMD

DATA

MDM

CDC

MIC RSVD RSVD RSVD RSVD RSVD

I/O

Status

Status

Data

Status

ADR

TAG X

4

CMD

DATA

5 6 7 8 9 10 11 12210 3

SYNC

Slot #

Figure 6. Compatible Implementation with Sample Rate Conversion Slots 3 and 4 Alternating

over Next Frame

Frame n

Frame n + 1

Frame n + 2

Frame n + 3

CMD

DATA

MDM

CDC

RSVD RSVD RSVD RSVD RSVD RSVD

I/O

Control

CMD

ADR

TAG X

X

CMD

DATA

MDM

CDC

MIC RSVD RSVD RSVD RSVD RSVD

I/O

Status

Status

Data

Status

ADR

TAG

CMD

DATA

MDM

CDC

RSVD RSVD RSVD RSVD RSVD RSVD

I/O

Control

CMD

Data

CMD

ADR

TAG X

X

CMD

DATA

MDM

CDC

MIC RSVD RSVD RSVD RSVD RSVD

I/O

Status

Status

Data

Status

ADR

TAG

4

CMD

DATA

5 6 7 8 9 10 11 12210 3

SYNC

Slot #