Intel® ICH5 AC ’97 Controller Theory of Operation

R

AC ’97 Programmer’s Reference Manual 19

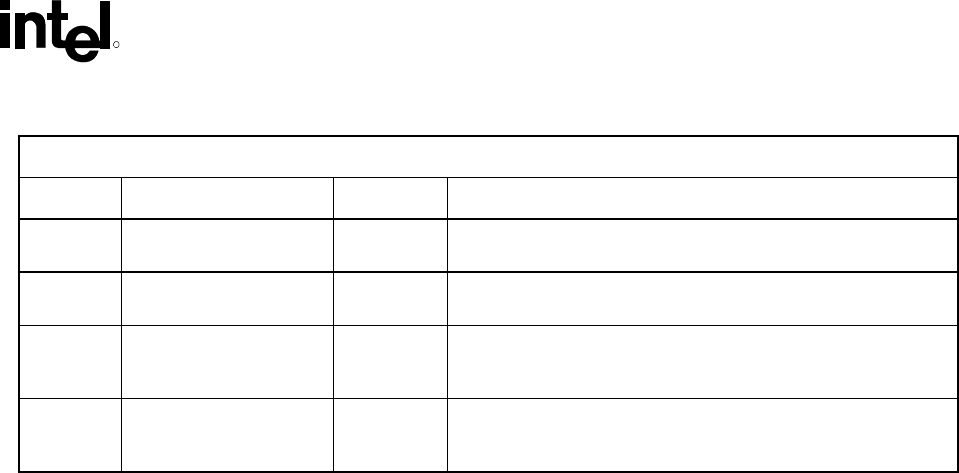

Table 4. Modem Registers

Device 31 Function 6 Modem

Offset Register Default Comments

04h-05h Command (COM) 0000h Bit 2: Bus Master Enable

Bit 0: I/O Space Enable

10h-13h Native Audio Mixer Base

Address

00000001h Address in the 64-K I/O space that allows 256 bytes of registers not

in conflict with any other set

14h - 17h Native Audio Bus

Mastering Base Address

(MBAR)

00000001h Address in the 64-K I/O space that allows 256 bytes of registers not

in conflict with any other set

3Ch Interrupt Line (INTLN) 00h A hardware interrupt (0-Fh) that follows value assigned to PIRQB#.

Has not effect on ICH5 it is used to indicate software the IRQ value

assigned to the device.

With the exception of register 41h on Device 31 Function 5, initialization of the PCI registers

above is the responsibility of the PnP capable OS. If a PnP OS is not available in the system, it is

then the BIOS’s responsibility to configure all PCI devices including the registers above.

Determination of the presence of PnP capable OS is usually made via a switch in the System

Setup. However, the final configuration or the existence or not of this switch is implementation

dependent.

The ICH5 AC’97 controllers also provide PCI Power Management functionality. PCI Power

Management Registers are available via the configuration space. Handling of the Power

Management registers is responsibility of the OS PCI Bus driver following standard procedures.

For further discussion on the usage model for this registers, refer to Section 3.6, Power

Management.

3.1.4 Hardware Interrupt Routing

The audio and modem functions in the ICH5 internally share the same PCI IRQ (PIRQB#). The

configuration software must take this into account and assign the same IRQ pin to both functions.

Sharing IRQs increases the ISR latencies. Each ISR must determine if the interrupting device is the

one serviced by the routine, as determined by the OS programming model. PIRQB# it is also

exposed as a PCI IRQ.

In an environment where a high Quality of Service (QoS) is required, system designers must pay

close attention to devices attached to the same PIRQ. Software driven signal processing functions,

as in the case of software driven modem and audio, require maintaining a low latency interrupt

service in order to maintain proper functionality. Software driver programmers need to pay close

attention to the ISR latencies and make use of Deferred Procedure Calls (DPC) as much as

possible.

3.1.5 PCI Lock

Note that host controllers are not required to support exclusive-access mechanisms (such as PCI

LOCK) for accesses to the memory-mapped register space. Therefore, if software attempts

exclusive-access mechanisms to the AC ’97 host controller memory-mapped register space, the

results are undefined.