Intel® ICH5 AC ’97 Controller Theory of Operation

R

28 AC ’97 Programmer’s Reference Manual

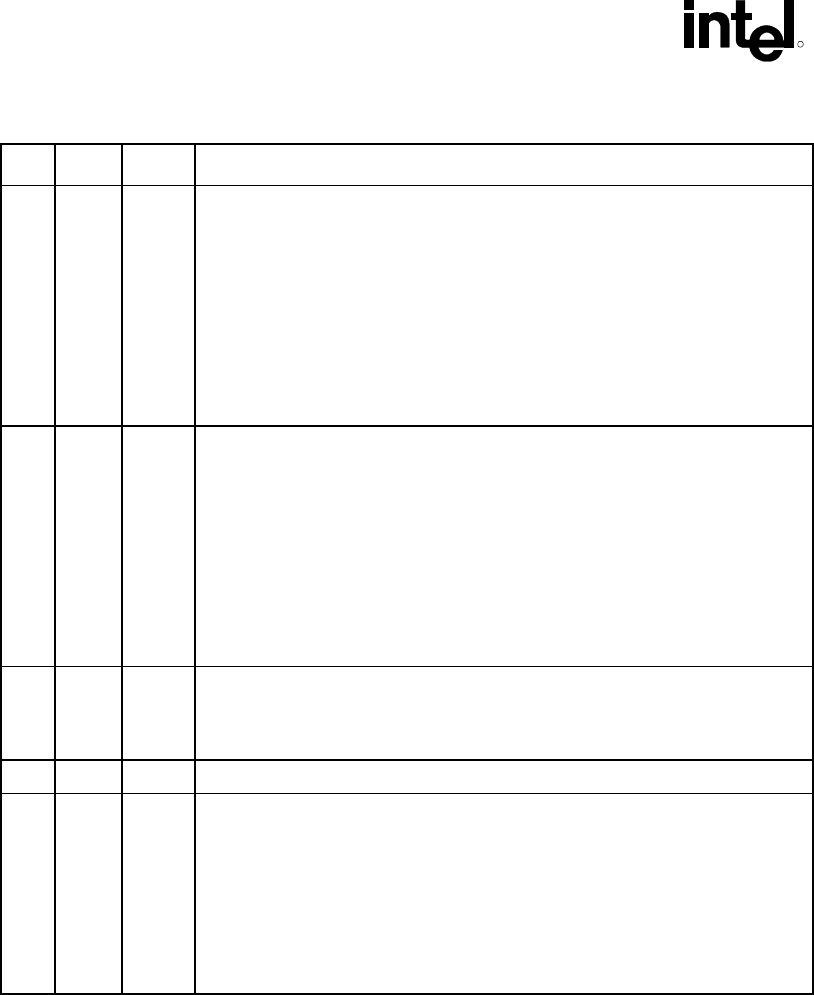

Table 12. SDM Register Description

Bit Type Reset Description

7:6 RW 00

PCM In 2, Microphone In 2 Data In Line (D21L): When the SE bit is set, these bits

indicate which SDATA_IN line should be used by the hardware for decoding the

input slots for PCM In 2 and Microphone In 2. When the SE bit is cleared, the value

of these bits is irrelevant, and PCM In 2 and Mic In 2 DMA engines are not

available.

00 SDATA_IN0

01 SDATA_IN1

10 SDATA_IN2

11 Reserved

5:4 RW 00

PCM In 1, Microphone In 1 Data In Line (DI1L): When the SE bit is set, these bits

indicates which SDATA_IN line should be used by the hardware for decoding the

input slots for PCM In 1 and Microphone In 1. When the SE bit is cleared, the value

of these bits are irrelevant, and the PCM In 1 and Mic In 1 engines use the OR’d

SDATA_IN lines.

00 SDATA_IN0

01 SDATA_IN1

10 SDATA_IN2

11 Reserved

3 RW 0

Steer Enable (SE): When set, the SDATA_IN lines are treated separately and not

OR’d together before being sent to the DMA engines. When cleared, the

SDATA_IN lines are OR’d together, and the “Microphone In 2” and “PCM In 2”

DMA engines are not available.

2 RO 0 Reserved

1:0 RO 00

Last Codec Read Data Input (LDI): When a codec register is read, this indicates

which SDATA_IN the read data returned on. Software can use this to determine

how the codecs are mapped. The values are:

00 SDATA_IN0

01 SDATA_IN1

10 SDATA_IN2

11 Reserved

3.5.1 Codec Register Shadowing

Codec register reads are presented in the AC-link in the next available frame after the controller

receives the I/O transaction. Data will be returned to the controller pending codec availability. To

avoid longer latencies than necessary, the codec must return data in the next available frame.

Multiple frame transactions impose large system latencies, to the detriment of system performance.

Even when data is returned in the frame immediately after the read request is presented in the AC-

link, the minimum latency is still on the order of 40 µs. To minimize the effect on the system

caused by long latencies in the AC-link, software drivers must maintain a copy of the codec

register in memory (shadow) and use this data instead of accessing the codec.