Intel® ICH5 AC ’97 Controller Theory of Operation

R

20 AC ’97 Programmer’s Reference Manual

3.2 DMA Engines

The ICH5 AC ’97 controller uses a scatter gather mechanism to access memory. There are five,

16-bit DMA engines for Audio: 2 PCM Stereo In, 2 MIC mono in, and S/P DIF Out. There is one,

20-bit PCM 2/4/6 channel surround DMA engine. There are two, 16-bit DMA engines for Modem:

In and Out. Audio and Modem registers are located in two separate PCI functions in the ICH5

components to allow for driver development flexibility.

3.2.1 Buffer Descriptor List

The Buffer Descriptor List (BDL) allows device drivers to program DMA transfer using the ICH5

controller. The BDL is an array of up to 32 entries, each of which describes a data buffer. Each

entry contains a pointer to a data buffer, control bits and the length expressed as the number of

samples contained in the data buffer. The buffer length is restricted to 65535 samples. Samples can

be either 16 or 20 bits. Refer to section 3.4.1, for more details on the layout of samples in the data

buffer. A value of “0” in the buffer length indicates no samples to process. Each descriptor can

point to a buffer of a different size.

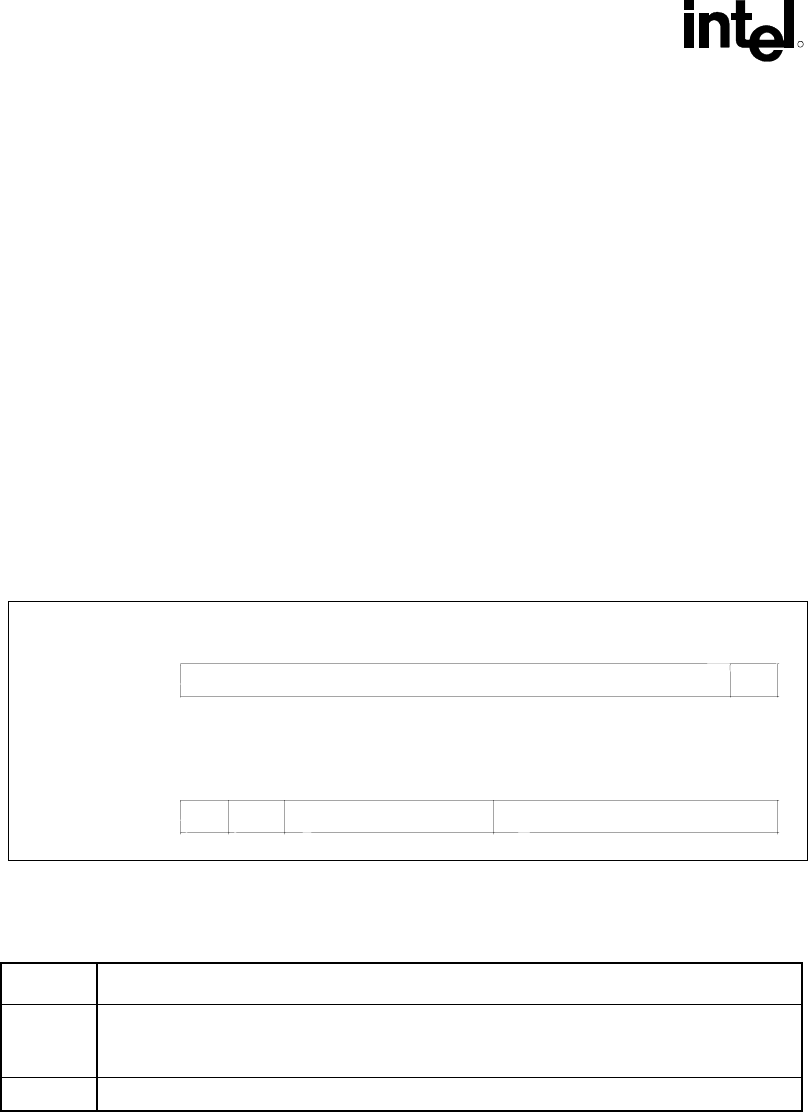

Figure 3. Generic Form of Buffer Descriptor (One Entry in the List)

(

Dword 0 : - 03h

)

31 1 0

Buffer Pointer 0

(

Dword 1 : - 07h

)

31 30 16 15 0

IOC BUP R Buffer Length

Table 5. BD Buffer Pointer (DWORD 0: 00-03h)

Bit Description

31:1 Buffer pointer. This field points to the location of the data buffer. Since the samples can be as

wide as 1 word, the buffer needs to be aligned to word boundaries to avoid having samples

straddle DWord boundaries.

0 Reserved. Must be 0 when writing this field.