Independent S-P/DIF Output Capability

R

AC ’97 Programmer’s Reference Manual 45

6 Independent S-P/DIF Output

Capability

The ICH5 AC’97 controller provides an independent DMA engine for S-P/DIF output that

operates independently of the six channels PCM Out stream. This allows the S-P/DIF data stream

to be independent of the PCM stream, allowing usage models such as playing a DVD movie with

output to S-P/DIF while at the same time using PCM In and Out in a telephony application.

The S-P/DIF DMA engine is initialized and is programmed in the same manner as the other DMA

engines available, as described in Section 3.2.

Data from the S-P/DIF DMA engine may be output on several different pairs of slots, depending

on the codec configuration. The SSM bits in the Global Control register control on which slots the

S/P-DIF data is transmitted, as defined below. The default value (00) for this register is a reserved

value, and so these bits must be appropriately programmed before the DMA engine is used.

These bits are reset on controller reset, and are not affected by the reset of the S-P/DIF DMA

engine.

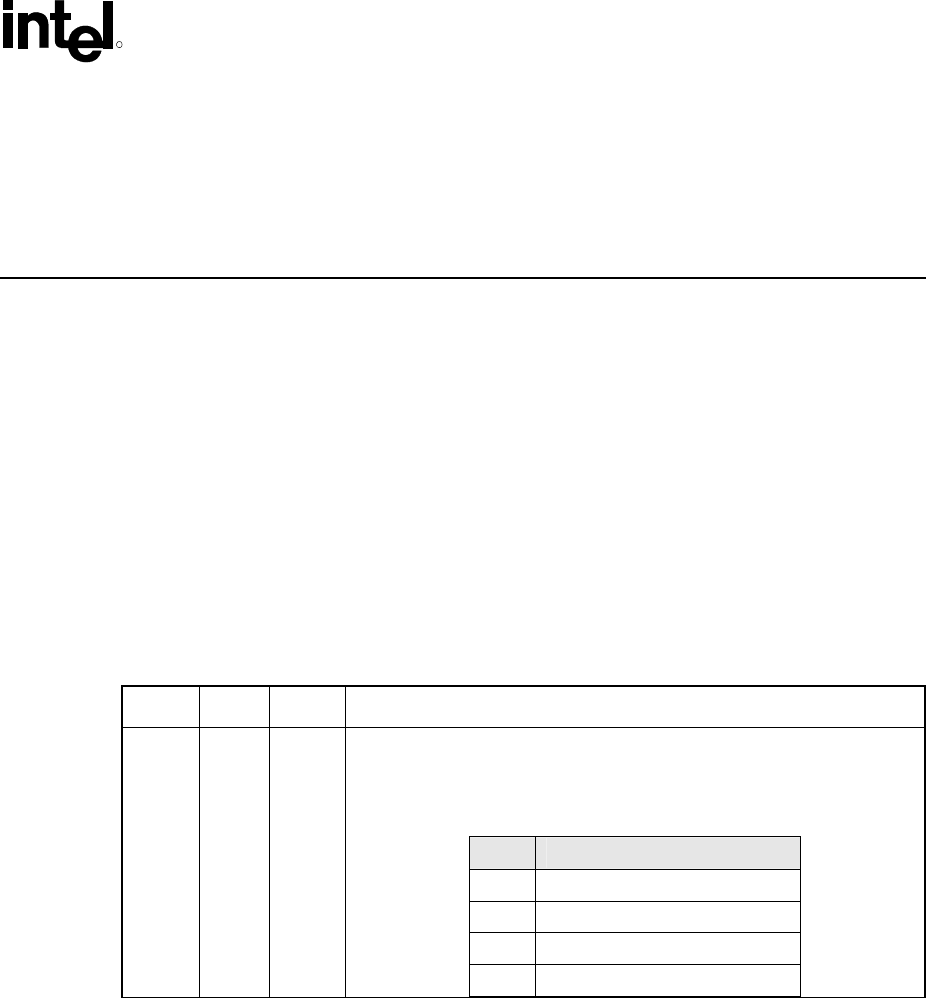

Table 25. Global Control Register S-P/DIF Slot Map Bits

Bit Type Reset Description

31:30 RW 00

S/PDIF Slot Map (SSM): If the run/pause bus master bit (bit 0 of offset

2Bh) is set, then the value in these bits indicate which slots S/PDIF data is

transmitted on. Software must ensure that the programming here does not

conflict with the PCM channels being used. If there is a conflict,

unpredictable behavior will result – the hardware will not check.

Bits Output Slots for S/PDIF Data

00 Reserved

01 7 & 8

10 6 & 9

11 10 & 11