S3F80P5_UM_ REV1.00 ELECTRICAL DATA

NOTE: The voltage gaps (LVD_GAPn (n=1~4)) between LVD and LVD FLAGn(n=1~4) have ± 80mV distribution. LVD and

LVD FLAGn(n=1~4) are not overlapped. The variation of LVD FLAGn(n=1~4) and LVD always is shifted in same

direction. That is, if one chip has positive tolerance (e.g. +50mV) in LVD FLAG, LVD has positive tolerance.

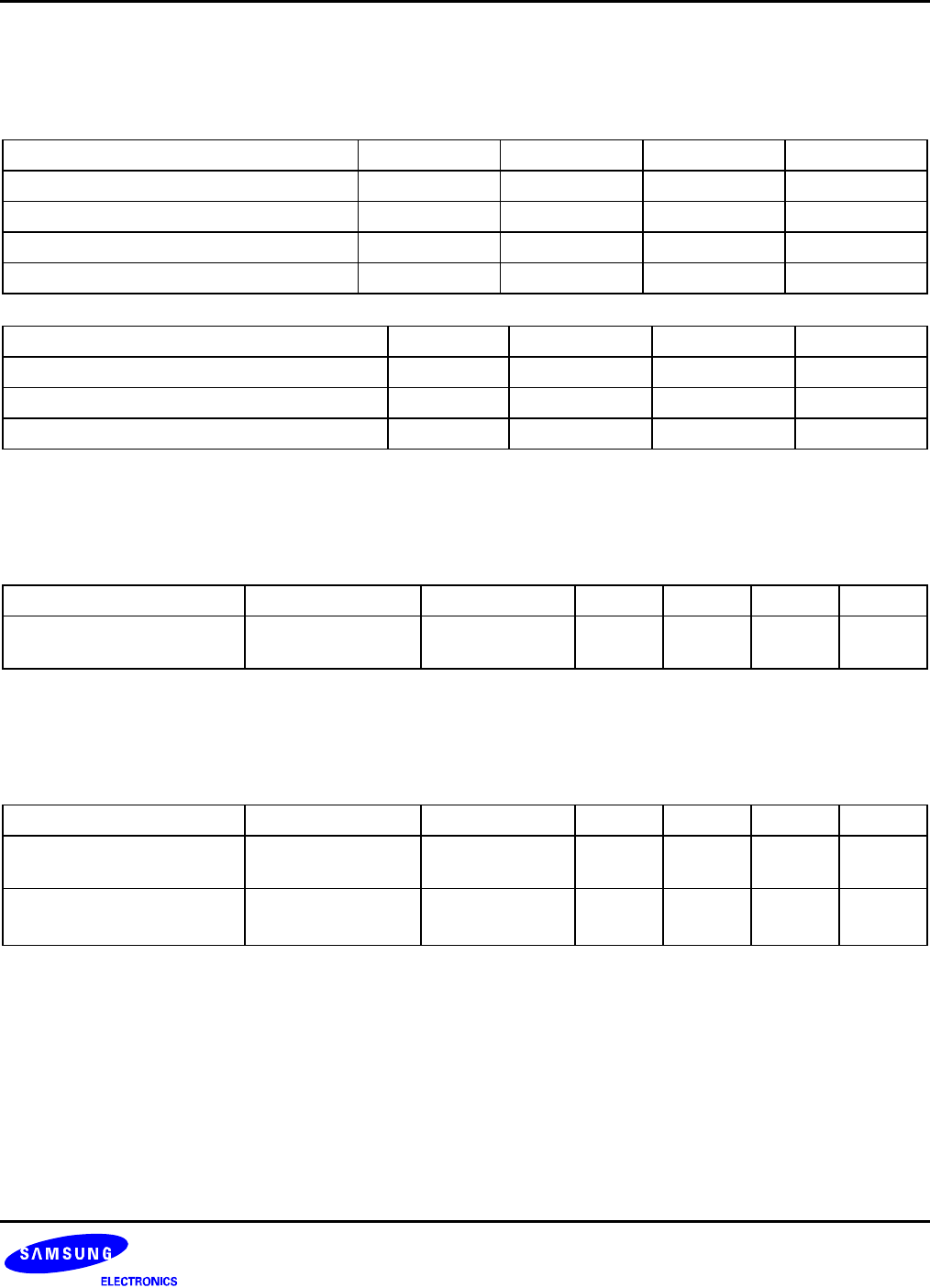

Symbol Min Typ Max Unit

LVD_GAP1 150 230 310 mV

LVD_GAP2 250 330 410 mV

LVD_GAP3 800 880 960 mV

LVD_GAP4 1000 1080 1160 mV

Symbol Min Typ Max Unit

GAP Between LVD_Flag1 and LVD_Flag2 50 100 150 mV

GAP Between LVD_Flag2 and LVD_Flag3 500 550 600 mV

GAP Between LVD_Flag3 and LVD_Flag4 150 200 250 mV

Table 16-4. Power On Reset Circuit

(T

A

= -25 °C to + 85 °C)

Parameter Symbol Conditions Min Typ Max Unit

Power on reset (POR)

Voltage

V

POR

−

0.8 1.1 1.4 V

Table 16-5. Data Retention Supply Voltage in Stop Mode

(T

A

= -25 °C to + 85 °C)

Parameter Symbol Conditions Min Typ Max Unit

Data Retention Supply

Voltage

V

DDDR

−

0.8

−

3.6 V

Data Retention Supply

Current

I

DDDR

V

DDDR

= 1.0 V

Stop Mode

− −

1

μA

NOTE: Data Retention Supply Current means that the minimum supplied current for data retention. When the

battery voltage is not sufficient (i,e, the supply current is <1uA), the data retention could be not be guaranteed.

16-5