Rev. 1.0, 07/01, page 94 of 372

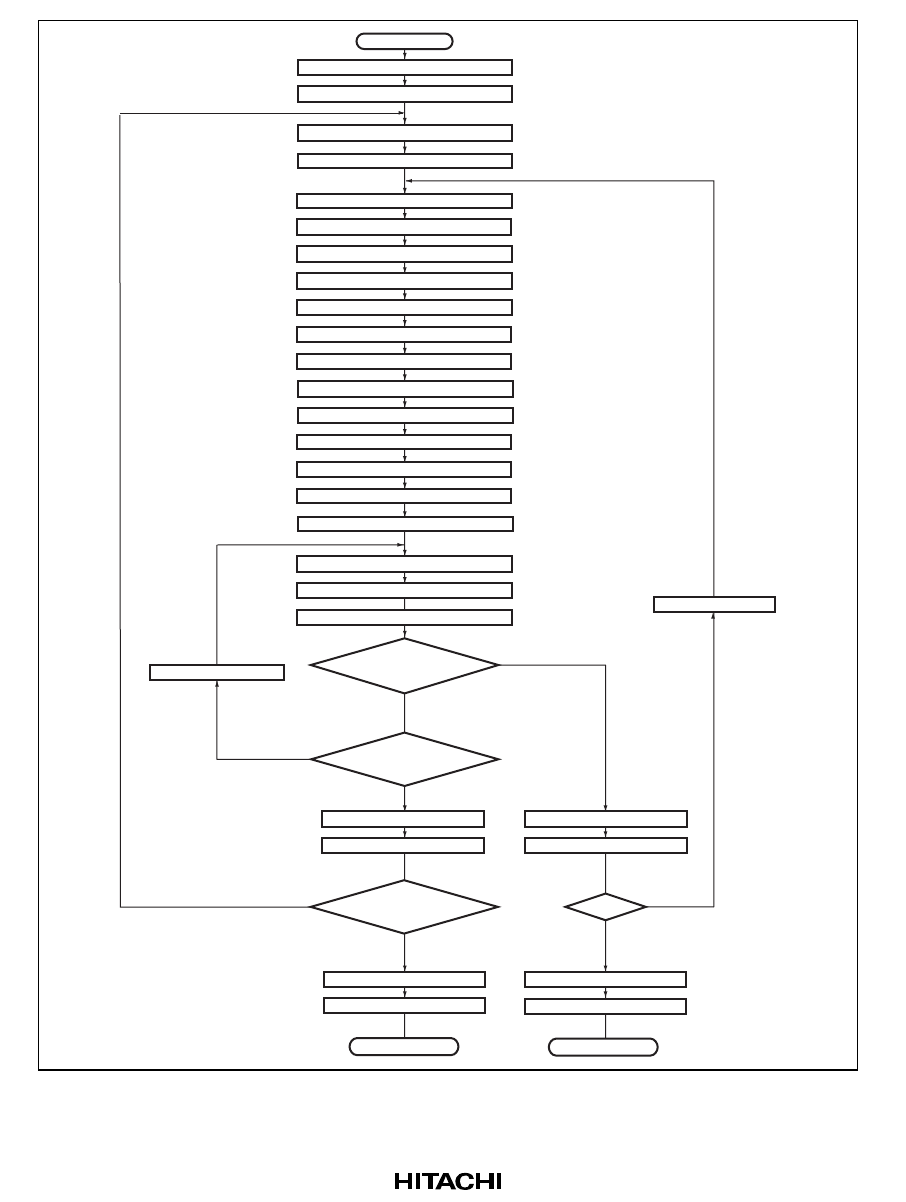

Erase start

Set EBR1

Enable WDT

Wait 1 µs

Wait 100 µs

Set SWE bit in FLMCR1 to 1

n = 1

Set ESU bit in FLMCR1 to 1

Set E bit to 1

Wait 10 µs

Clear E bit to 0

Wait 10 µs

Clear ESU bit in FLMCR1 to 0

10 µs

Disable WDT

Read verify data

Increment address

Verify data = all 1s ?

Last address of block ?

All erase blocks erased ?

Set block start address as verify address

H'FF dummy write to verify address

Wait 20 µs

Wait 2 µs

Set EV bit to 1

Wait 100 µs

End of erasing

Clear SWE bit to 0

Wait 4 µs

Clear EV bit to 0

n ≤100 ?

Wait 100 µs

Erasing failure

Clear SWE bit to 0

Wait 4µs

Clear EV bit to 0

n ← n + 1

Ye s

No

Ye s

Ye s

Ye s

Ye s

No

No

No

Figure 7-4 Erase/Erase-Verify Flowchart