Rev. 1.0, 07/01, page 100 of 372

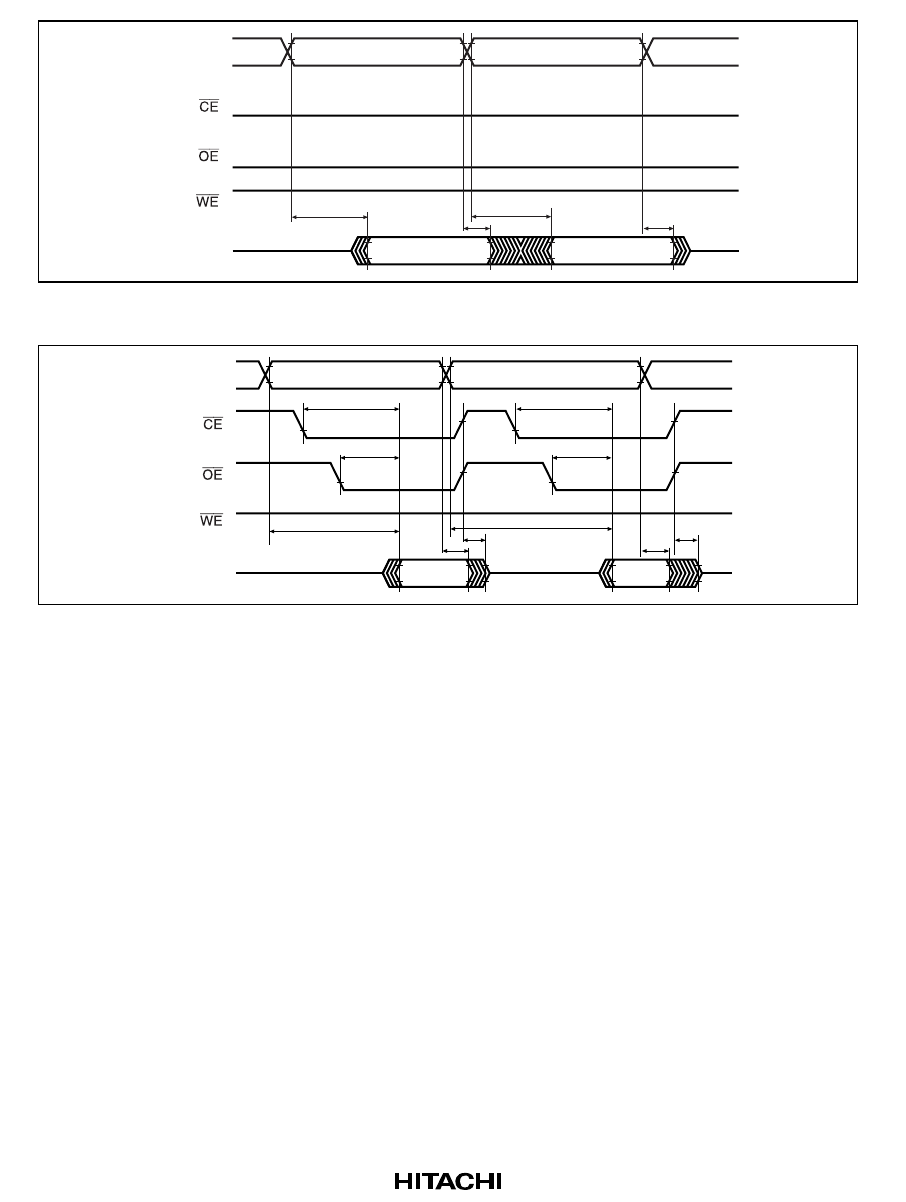

A15–A0

I/O7–I/O0

t

acc

t

acc

t

oh

t

oh

Address stableAddress stable

Figure 7-8 CE and OE Enable State Read Timing Waveforms

A15–A0

I/O7–I/O0

t

acc

t

ce

t

oe

t

oe

t

ce

t

acc

t

oh

t

df

t

df

t

oh

Address stableAddress stable

Figure 7-9 CE and OE Clock System Read Timing Waveforms

7.6.4 Auto-Program Mode

1. When reprogramming previously programmed addresses, perform auto-erasing before auto-

programming.

2. Perform auto-programming once only on the same address block. It is not possible to program

an address block that has already been programmed.

3. In auto-program mode, 128 bytes are programmed simultaneously. This should be carried out

by executing 128 consecutive byte transfers. A 128-byte data transfer is necessary even when

programming fewer than 128 bytes. In this case, H'FF data must be written to the extra

addresses.

4. The lower 7 bits of the transfer address must be low. If a value other than an effective address

is input, processing will switch to a memory write operation but a write error will be flagged.

5. Memory address transfer is performed in the second cycle (figure 7-10). Do not perform

transfer after the third cycle.

6. Do not perform a command write during a programming operation.