Rev. 1.0, 07/01, page 57 of 372

Section 4 Address Break

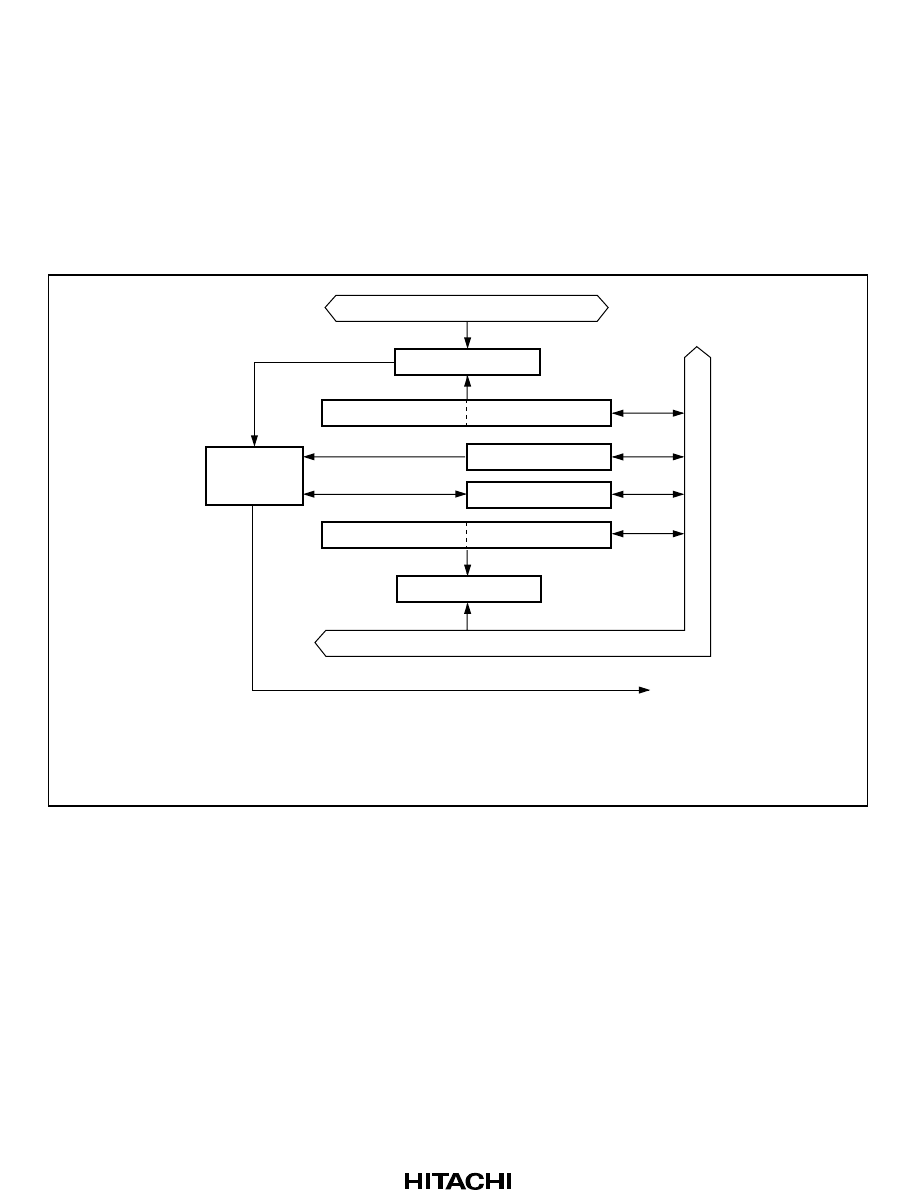

The address break simplifies on-board program debugging. It requests an address break interrupt

when the set break condition is satisfied. The interrupt request is not affected by the I bit of CCR.

Break conditions that can be set include instruction execution at a specific address and a

combination of access and data at a specific address. With the address break function, the

execution start point of a program containing a bug is detected and execution is branched to the

correcting program. Figure 4-1 shows a block diagram of the address break.

BARH BARL

BDRH BDRL

ABRKCR

ABRKSR

Internal address bus

Comparator

Interrupt

generation

control circuit

Internal data bus

Comparator

Interrupt

Legend:

BARH, BARL: Break address register

BDRH, BDRL: Break data register

ABRKCR: Address break control register

ABRKSR: Address break status register

Figure 4-1 Block Diagram of an Address Break

4.1 Register Descriptions

Address break has the following registers. For details on register addresses and register states

during each processing, refer to section 19, Internal I/O Register.

•

Address break control register(ABRKCR)

•

Address break status register(ABRKSR)

•

Break address register(BARH, BARL)

•

Break data register(BDRH, BDRL)

ABK0001A0000_000020010700