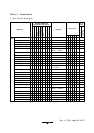

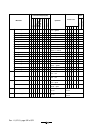

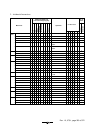

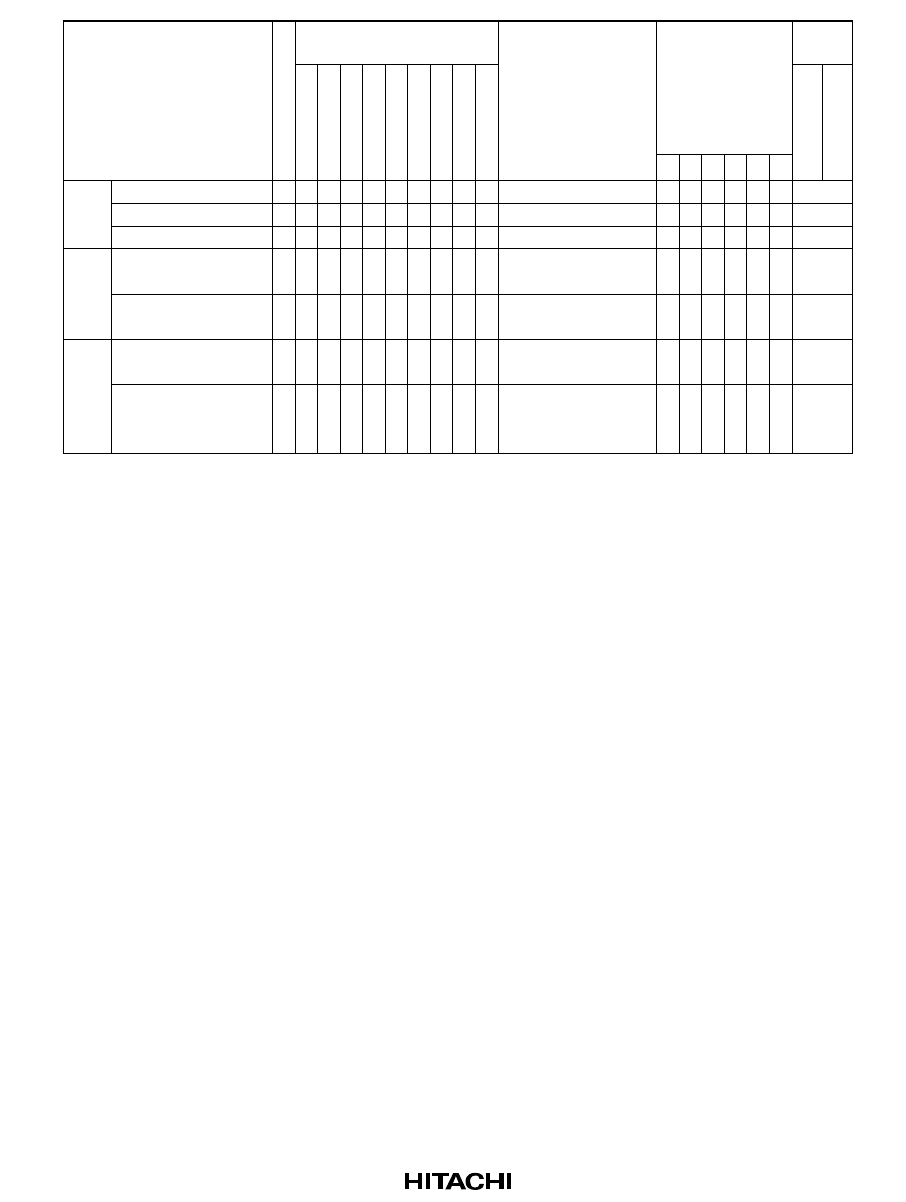

Rev. 1.0, 07/01, page 325 of 372

Mnemonic Operation

Operand Size

Addressing Mode and

Instruction Length (bytes)

No. of

States

*1

Condition Code

IHNZVC

#xx

Rn

@ERn

@(d, ERn)

@–ERn/@ERn+

@aa

@(d, PC)

@@aa

—

NEG.B Rd

NEG.W Rd

NEG.L ERd

EXTU.W Rd

EXTU.L ERd

EXTS.W Rd

EXTS.L ERd

0–Rd8 → Rd8

0–Rd16 → Rd16

0–ERd32 → ERd32

0 → (<bits 15 to 8>

of Rd16)

0 → (<bits 31 to 16>

of ERd32)

(<bit 7> of Rd16) →

(<bits 15 to 8> of Rd16)

(<bit 15> of ERd32) →

(<bits 31 to 16> of

ERd32)

B

W

L

W

L

W

L

2

2

2

2

2

2

2

—

—

—

—

—

—

—

—

—

—

—

2

2

2

2

2

2

2

Normal

Advanced

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

0

0

0

0

0

0

—

—

—

—

↔↔↔↔

↔↔

NEG

EXTU

EXTS