Rev. 1.0, 07/01, page 323 of 372

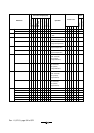

2. Arithmetic Instructions

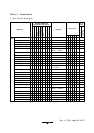

Mnemonic

Operand Size

Addressing Mode and

Instruction Length (bytes)

No. of

States

*1

Condition Code

IHNZVC

#xx

Rn

@ERn

@(d, ERn)

@–ERn/@ERn+

@aa

@(d, PC)

@@aa

—

ADD.B #xx:8, Rd

ADD.B Rs, Rd

ADD.W #xx:16, Rd

ADD.W Rs, Rd

ADD.L #xx:32, ERd

ADD.L ERs, ERd

ADDX.B #xx:8, Rd

ADDX.B Rs, Rd

ADDS.L #1, ERd

ADDS.L #2, ERd

ADDS.L #4, ERd

INC.B Rd

INC.W #1, Rd

INC.W #2, Rd

INC.L #1, ERd

INC.L #2, ERd

DAA Rd

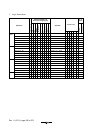

SUB.B Rs, Rd

SUB.W #xx:16, Rd

SUB.W Rs, Rd

SUB.L #xx:32, ERd

SUB.L ERs, ERd

SUBX.B #xx:8, Rd

SUBX.B Rs, Rd

SUBS.L #1, ERd

SUBS.L #2, ERd

SUBS.L #4, ERd

DEC.B Rd

DEC.W #1, Rd

DEC.W #2, Rd

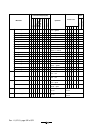

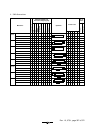

Operation

Rd8+#xx:8 → Rd8

Rd8+Rs8 → Rd8

Rd16+#xx:16 → Rd16

Rd16+Rs16 → Rd16

ERd32+#xx:32 →

ERd32

ERd32+ERs32 →

ERd32

Rd8+#xx:8 +C → Rd8

Rd8+Rs8 +C → Rd8

ERd32+1 → ERd32

ERd32+2 → ERd32

ERd32+4 → ERd32

Rd8+1 → Rd8

Rd16+1 → Rd16

Rd16+2 → Rd16

ERd32+1 → ERd32

ERd32+2 → ERd32

Rd8 decimal adjust

→ Rd8

Rd8–Rs8 → Rd8

Rd16–#xx:16 → Rd16

Rd16–Rs16 → Rd16

ERd32–#xx:32 → ERd32

ERd32–ERs32 → ERd32

Rd8–#xx:8–C → Rd8

Rd8–Rs8–C → Rd8

ERd32–1 → ERd32

ERd32–2 → ERd32

ERd32–4 → ERd32

Rd8–1 → Rd8

Rd16–1 → Rd16

Rd16–2 → Rd16

B

B

W

W

L

L

B

B

L

L

L

B

W

W

L

L

B

B

W

W

L

L

B

B

L

L

L

B

W

W

2

4

6

2

4

6

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

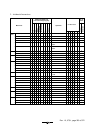

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

(1)

(1)

(2)

(2)

—

—

—

—

—

—

—

—

*

(1)

(1)

(2)

(2)

—

—

—

—

—

—

2

2

4

2

6

2

2

2

2

2

2

2

2

2

2

2

2

2

4

2

6

2

2

2

2

2

2

2

2

2

Normal

Advanced

↔

↔

↔

↔↔↔↔↔↔

↔↔↔↔↔↔↔

—

—

—

—

—

—

↔↔↔↔↔↔↔↔↔↔↔↔↔

↔↔↔↔↔

(3)

(3)

—

—

—

(3)

(3)

—

—

—

↔↔↔

↔↔↔↔↔↔↔↔↔

↔↔↔↔↔↔

—

—

—

*

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

↔

↔

↔

↔

↔

↔

↔

↔

↔↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔↔↔↔↔

↔

↔

↔

↔

↔↔↔

↔↔↔

↔↔↔

ADD

ADDX

ADDS

INC

DAA

SUB

SUBX

SUBS

DEC