Rev. 1.0, 07/01, page 12 of 372

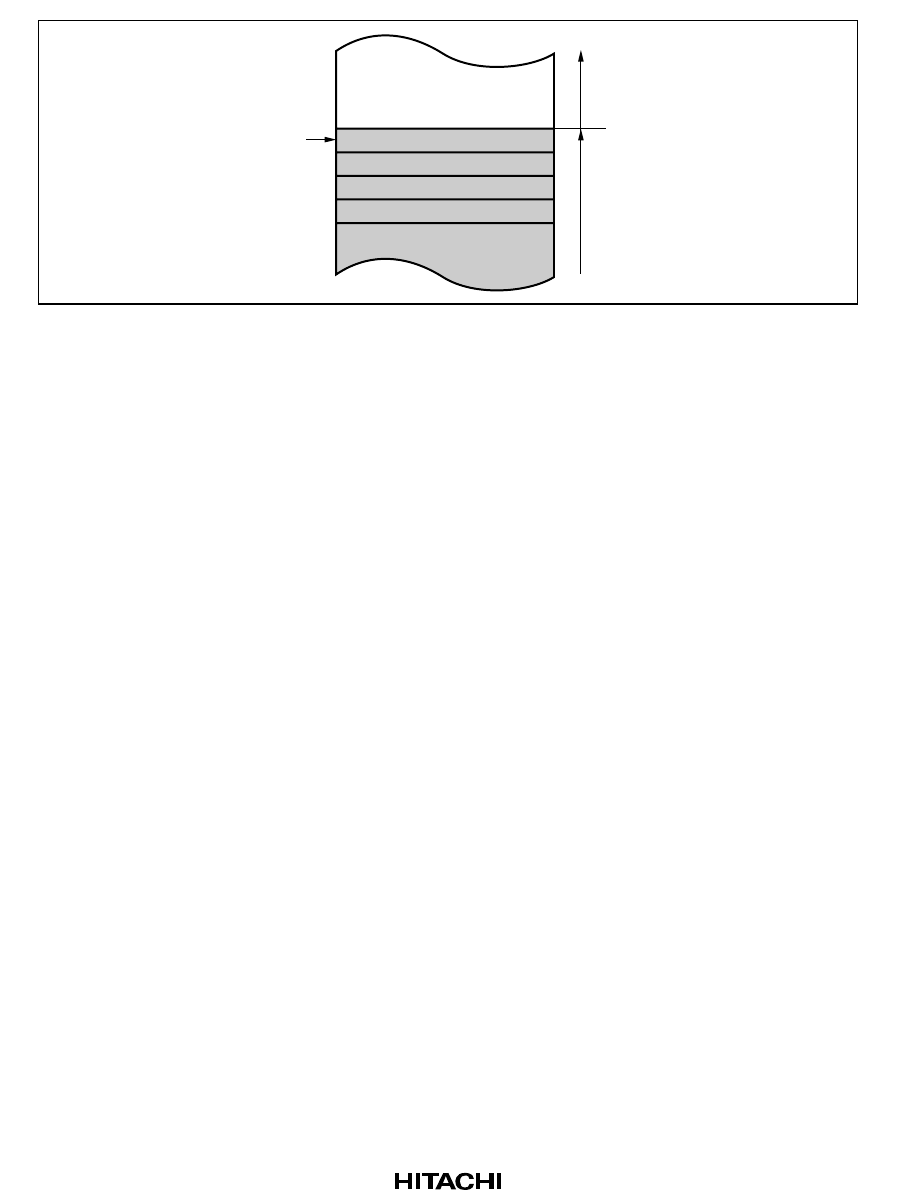

SP (ER7)

Free area

Stack area

Figure 2-4 Relationship between Stack Pointer and Stack Area

2.2.2 Program Counter (PC)

This 24-bit counter indicates the address of the next instruction the CPU will execute. The length

of all CPU instructions is 2 bytes (one word), so the least significant PC bit is ignored. (When an

instruction is fetched, the least significant PC bit is regarded as 0). The PC is initialized when the

start address is loaded by the vector address generated during reset exception-handling sequence.

2.2.3 Condition-Code Register (CCR)

This 8-bit register contains internal CPU status information, including an interrupt mask bit (I) and

half-carry (H), negative (N), zero (Z), overflow (V), and carry (C) flags. The I bit is initialized to 1

by reset exception-handling sequence, but other bits are not initialized.

Some instructions leave flag bits unchanged. Operations can be performed on the CCR bits by the

LDC, STC, ANDC, ORC, and XORC instructions. The N, Z, V, and C flags are used as branching

conditions for conditional branch (Bcc) instructions.

For the action of each instruction on the flag bits, see appendix A.1 Instruction List.