Rev. 1.0, 07/01, page 225 of 372

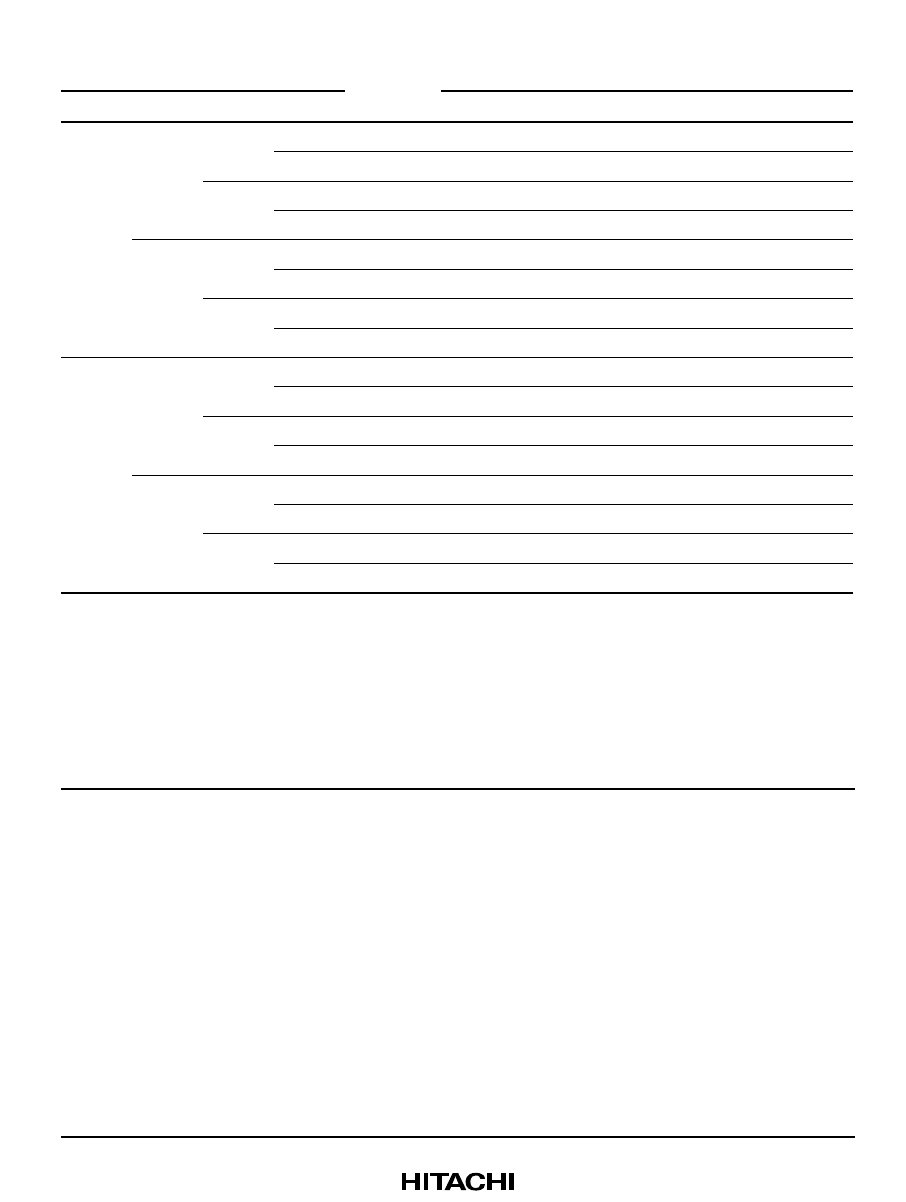

Table 15-2 Transfer Rate

Bit 3 Bit 2 Bit 1 Bit 0 Transfer Rate

CKS3 CKS2 CKS1 CKS0

Clock

φ=5 MHz φ=8 MHz φ=10 MHz φ=16 MHz

0 φ/28 179 kHz 286 kHz 357 kHz 571 kHz0

1 φ/40 125 kHz 200 kHz 250 kHz 400 kHz

0 φ/48 104 kHz 167 kHz 208 kHz 333 kHz

0

1

1 φ/64 78.1 kHz 125 kHz 156 kHz 250 kHz

0 φ/80 62.5 kHz 100 kHz 125 kHz 200 kHz0

1 φ/100 50.0 kHz 80.0 kHz 100 kHz 160 kHz

0 φ/112 44.6 kHz 71.4 kHz 89.3 kHz 143 kHz

0

1

1

1 φ/128 39.1 kHz 62.5 kHz 78.1 kHz 125 kHz

0 φ/56 89.3 kHz 143 kHz 179 kHz 286 kHz0

1 φ/80 62.5 kHz 100 kHz 125 kHz 200 kHz

0 φ/96 52.1 kHz 83.3 kHz 104 kHz 167 kHz

0

1

1 φ/128 39.1 kHz 62.5 kHz 78.1 kHz 125 kHz

0 φ/160 31.3 kHz 50.0 kHz 62.5 kHz 100 kHz0

1 φ/200 25.0 kHz 40.0 kHz 50.0 kHz 80.0 kHz

0 φ/224 22.3 kHz 35.7 kHz 44.6 kHz 71.4 kHz

1

1

1

1 φ/256 19.5 kHz 31.3 kHz 39.1 kHz 62.5 kHz

15.3.2 I

2

C Bus Control Register 2 (ICCR2)

ICCR1 is an 8-bit readable/writable register that issues start/stop conditions, manipulates the SDA

pin, monitors the SCL pin, and controls reset in I

2

C control part.

Bit Bit Name Initial Value R/W Description

7 BBSY 0 R/W Bus Busy

This bit enables to confirm whether the I

2

C bus is occupied

or released and to issue start/stop conditions in master

mode. With the clocked synchronous serial format, this bit

has no meaning. With the I

2

C bus format, this bit is set to 1

when the SDA level changes from high to low under the

condition of SCL = high, assuming that the start condition

has been issued. This bit is cleared to 0 when the SDA

level changes from low to high under the condition of SCL

= high, assuming that the stop condition has been issued.

Write 1 to BBSY and 0 to SCP to issue a start condition.

Follow this procedure when also re-transmitting a start

condition. Write 0 in BBSY and 0 in SCP to issue a stop

condition. To issue start/stop conditions, use the MOV

instruction.