Intel

®

NetStructure

TM

ZT 7102 Chassis Management Module

Built-In Self Test

48 Technical Product Specification

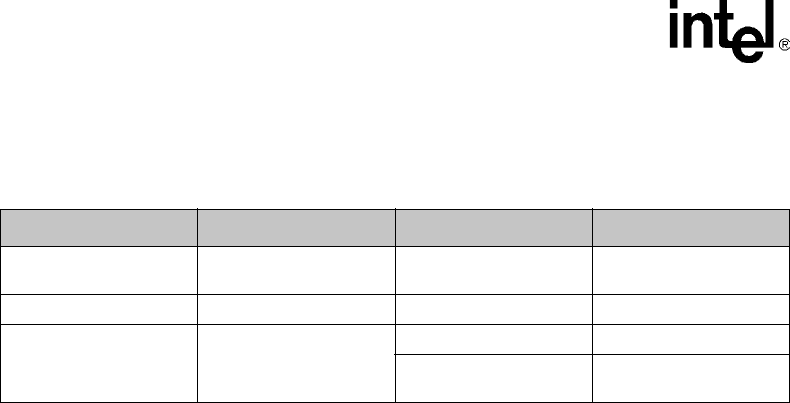

The BIST is broken down into stages consisting of groups of tests run at serious times throughout

the boot process. Table 20 shows the different BIST stages and the tests associated with each stage:

6.2 Boot-BIST

The codes in Boot-BIST will be executed at the very early stage of the RedBoot bootstrap, which is

just before the FPGA programming and memory module initialization. Boot-BIST will perform

checksum checking over the RedBoot image and the FPGA image. Checksum errors will be

detected if there is a mismatch of between the calculated checksum and the stored checksum in FIS

directory.

Boot-BIST will also perform a Base Memory Test for the first 1 Mbyte of memory. Whenever there

is an error, BIST will inform the user by prompting a warning message through the console

terminal and log the event to event-log area.

6.3 Early-BIST

The early BIST stage will extend the reset timeout period on the watchdog timer (MAX6374) by

strobing GPIO7 on FPGA1. This prevents any possible hardware reset during the BIST process.

The watchdog timer will be enabled after the ADM1026 GPIO initialization, and disabled once it

reaches the RedBoot console. The OS will enable the watchdog timer again and start the strobing

thread at the kernel level.

6.4 Mid-BIST

Mid-BIST will be started just after some basic modules initialization, such as flash and zlib

compression. In this stage of BIST, the Extended Memory Test will be performed to scan and

diagnose the possible bit errors in the memory. It starts scanning from 1 MByte to the maximum

available memory size on the board. It will not test the memory below 1 MByte because portion of

RedBoot has already loaded and resided on it. The memory test includes: the walking ones test,

32-bit address test, and 32-bit inverse address test. Furthermore, voltage and temperature ratings

will be verified to lie within the hardware tolerable ranges. The FPGA firmware version will be

checked and will alert if an older version of an FPGA image has been detected. Also, system date

and time will be read out from the real time clock and displayed through the console terminal. NIC

presence is also checked here. NIC self-test is not performed here because it is performed in the

existing NIC driver module.

Table 20. BIST Implementation

Boot-BIST Early-BIST Mid-BIST Late-BIST

RedBoot image

checksum

Strobe watchdog timer to

extend timeout period

Extended memory test BlueCat image checksum

FPGA image checksum FPGA version check IPMB bus test

Base memory test

DS1307 RTC test

Local PCI bus / NIC

presence test