Rev. 1.0, 07/01, page 171 of 372

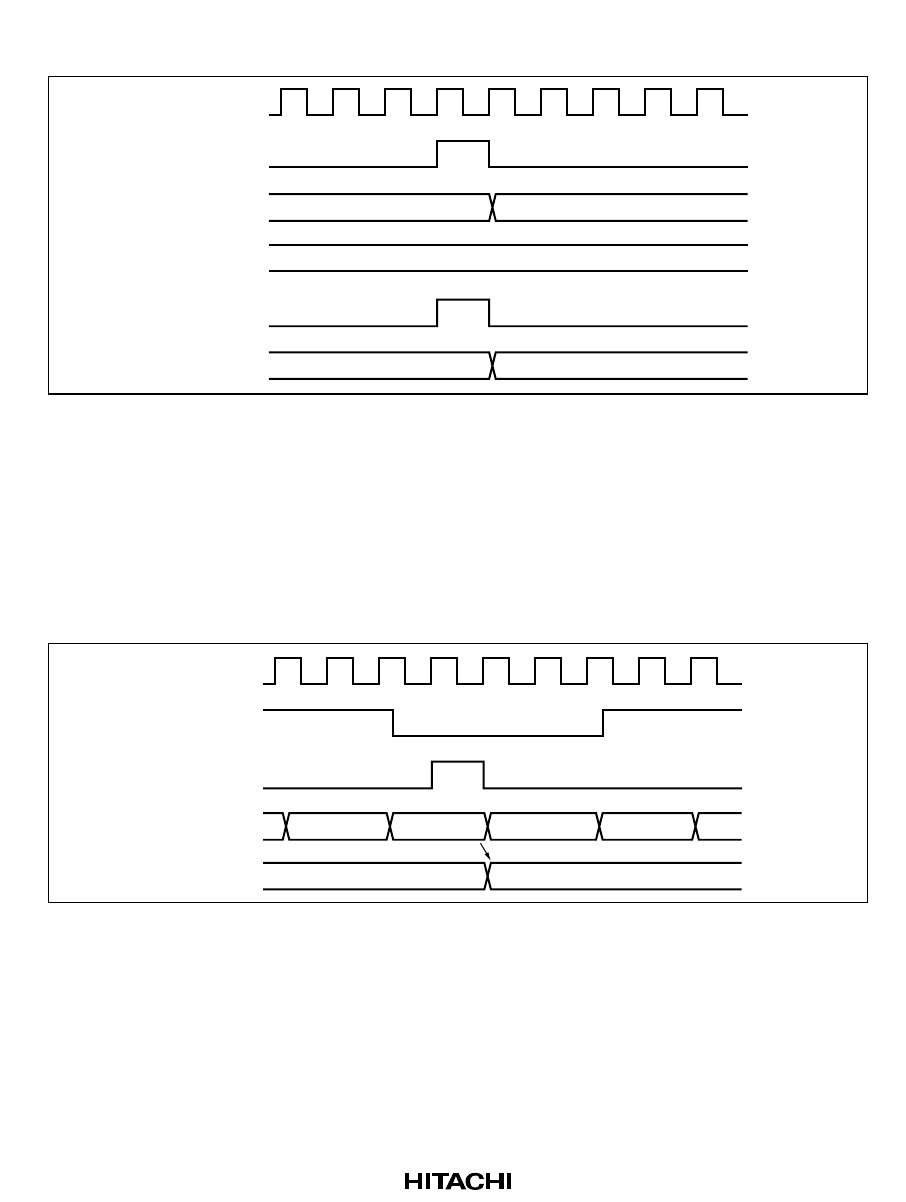

Figure 12-16 shows the output compare timing.

GRA to GRD

TCNT

TCNT input

clock

φ

N

N N+1

Compare

match signal

FTIOA to FTIOD

Figure 12-16 Output Compare Output Timing

12.5.3 Input Capture Timing

Input capture on the rising edge, falling edge, or both edges can be selected through settings in

TIOR0 and TIOR1. Figure 12-17 shows the timing when the falling edge is selected. The pulse

width of the input capture signal must be at least two system clock (φ) cycles; shorter pulses will

not be detected correctly.

TCNT

Input capture

input

ø

N–1 N N+1 N+2

N

GRA to GRD

Input capture

signal

Figure 12-17 Input Capture Input Signal Timing