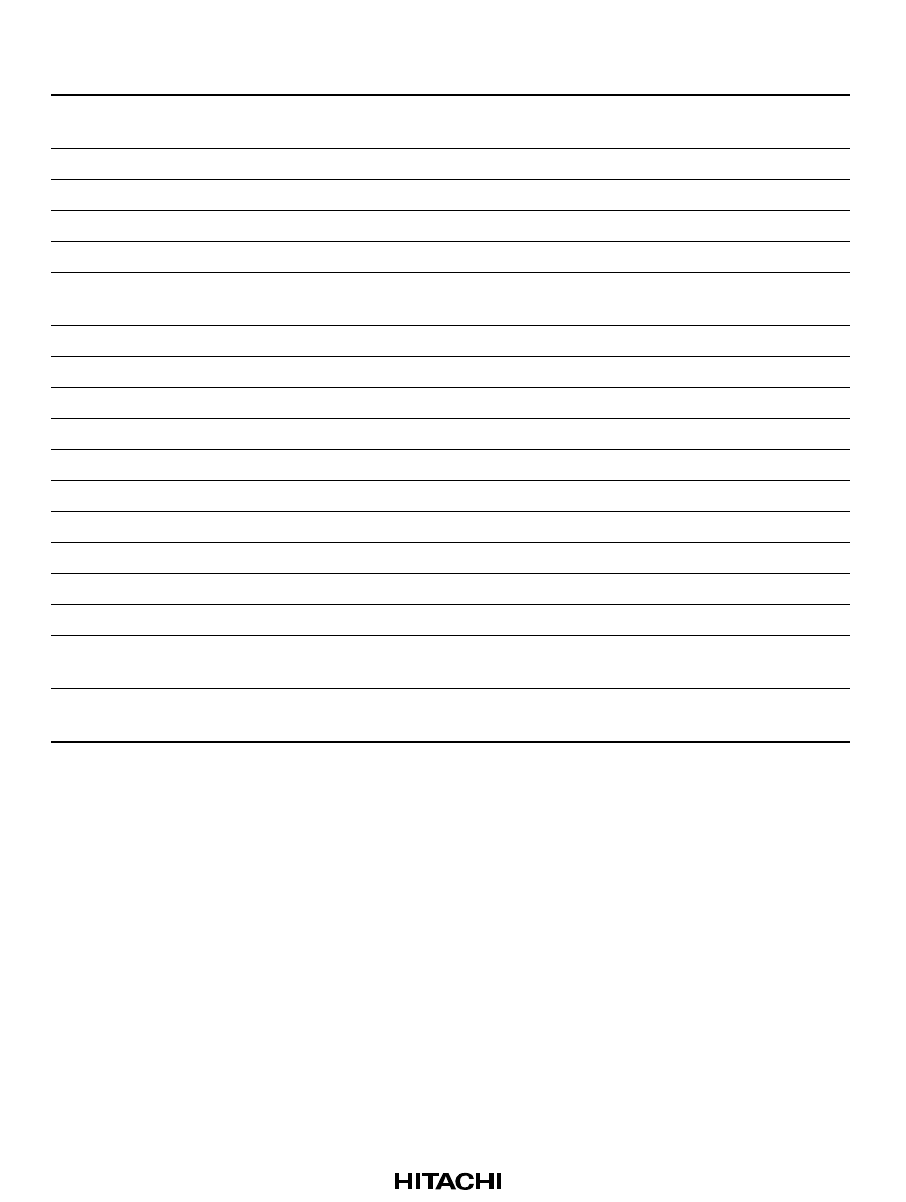

Rev. 1.0, 07/01, page 278 of 372

Register Name

Abbre-

viation Bit No Address

Module

Name

Data

Bus

Width

Access

State

———

H'FFE6,

H'FFE7

I/O port

——

Port control register 5 PCR5 8 H'FFE8 I/O port 8 2

———

H'FFE9 I/O port

——

Port control register 7 PCR7 8 H'FFEA I/O port 8 2

Port control register 8 PCR8 8 H'FFEB I/O port 8 2

———

H'FFEC to

H'FFEF

I/O port

——

System control register 1 SYSCR1 8 H'FFF0 Power-down 8 2

System control register 2 SYSCR2 8 H'FFF1 Power-down 8 2

Interrupt edge select register 1 IEGR1 8 H'FFF2 Interrupts 8 2

Interrupt edge select register 2 IEGR2 8 H'FFF3 Interrupts 8 2

Interrupt enable register 1 IENR1 8 H'FFF4 Interrupts 8 2

———

H'FFF5 I/O port

——

Interrupt flag register 1 IRR1 8 H'FFF6 Interrupts 8 2

———

H'FFE7 I/O port

——

Wake-up interrupt flag register IWPR 8 H'FFF8 Interrupts 8 2

Module standby control register 1 MSTCR1 8 H'FFF9 Power-down 8 2

———

H'FFEA,

H'FFFB

Power-down

——

———

H'FFFC to

H'FFFF

——

Notes: 1. LVDC : Low-voltage detection circuits (optional)

2. Only word access can be used.

3. WDT: Watchdog timer.