Rev. 1.0, 07/01, page 34 of 372

2.6.2 On-Chip Peripheral Modules

On-chip peripheral modules are accessed in two states or three states. The data bus width is 8 bits

or 16 bits depending on the register. For description on the data bus width and number of

accessing states of each register, refer to section 19, Internal I/O Registers. Registers with 16-bit

data bus width can be accessed by word size only. Registers with 8-bit data bus width can be

accessed by byte or word size. When a register with 8-bit data bus width is accessed by word size,

access is completed in two cycles. In two-state access, the operation timing is the same as that for

on-chip memory.

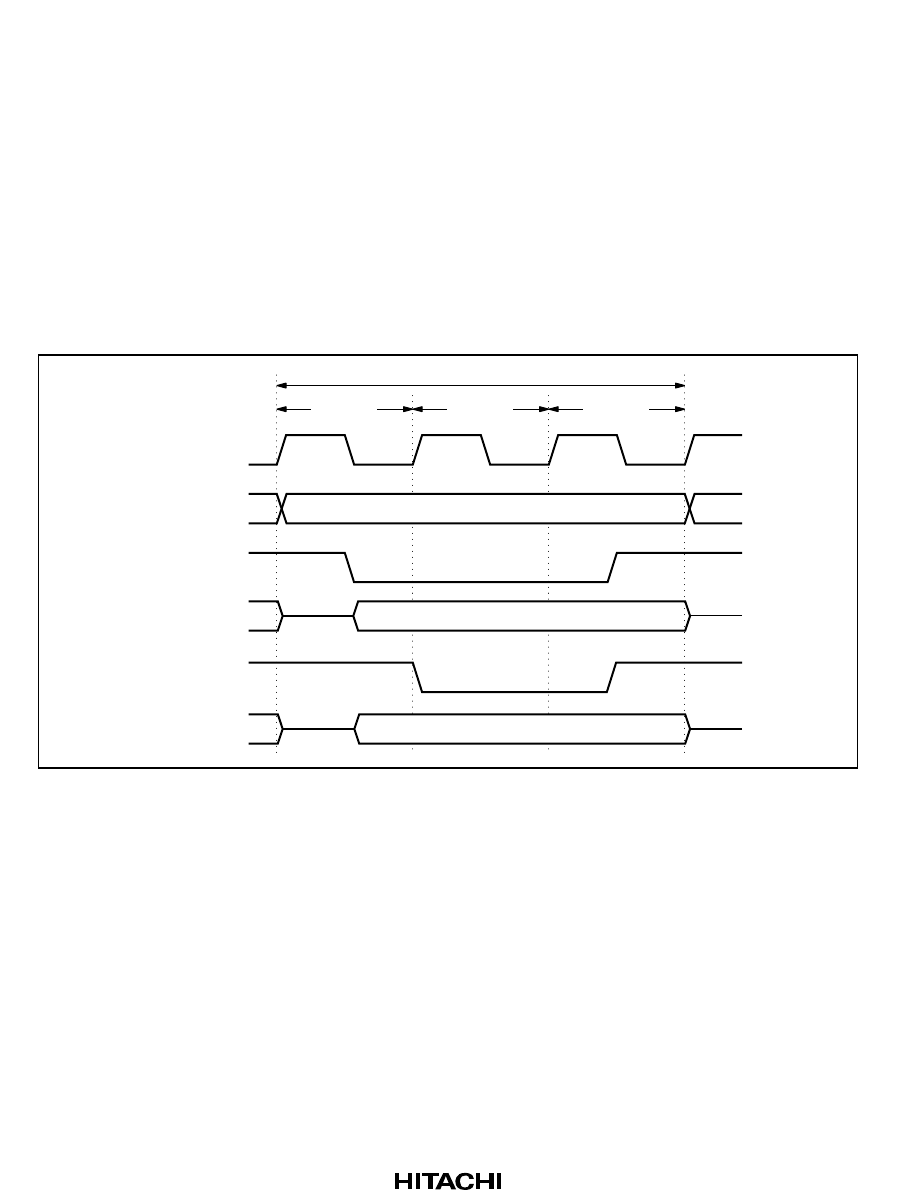

Figure 2-10 shows the operation timing in the case of three-state access to an on-chip peripheral

module.

T

1

state

Bus cycle

Internal

address bus

Internal

read signal

Internal

data bus

(read access)

Internal

write signal

Read data

Address

Internal

data bus

(write access)

T

2

state T

3

state

Write data

SUB

ø or ø

Figure 2-10 On-Chip Peripheral Module Access Cycle (3-State Access)