176

CHAPTER 8 Programmable Pulse Generator (PPG0, 1)

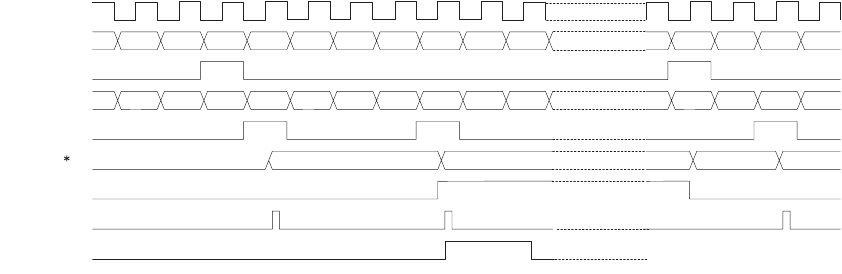

Figure 8.5-3 Operation timing of PPG

■ Start Operation of PPG

The PPG starts operation by setting "1" to the start bit. The initial operation is performed as follow.

• Clears the relative counter and loads the initial address in synchronization with the falling edge of the

FRC clock after starting.

• Reads the frame data indicated by the initial address, sets data to each latch of OTD and ODL, and the

status will be compare match wait for the OTD value and relative counter value.

• When compare match is detected, transfers the ODL value to the output latch (OUTL) in

synchronization with rising edge of the FRC clock, reads the next frame data, then updates each latch

value of OTD and ODL, while the status is compare match wait. (This operation is performed

repeatedly.)

■ Update Timing Data Register

When timing data is updated during PPG operation, the next data should be written after FRC3 x 2 or

longer has passed after writing the register.

■ Precaution when Clear IF Flag

Do not perform clearing of IF flag and interrupt enable (IE=1) concurrently. Enables interrupts after

clearing the IF flag.

XX XX

00

0

10203040506 00010203

F1 F2 FX F1

Wclr

IFlag

IRQ.STB

PPG.IEN

PPG.OUT

CNT. EQ. OTD

Relativity

counter value

FRC. EQ. TD

FC4-19R

FRC3

07