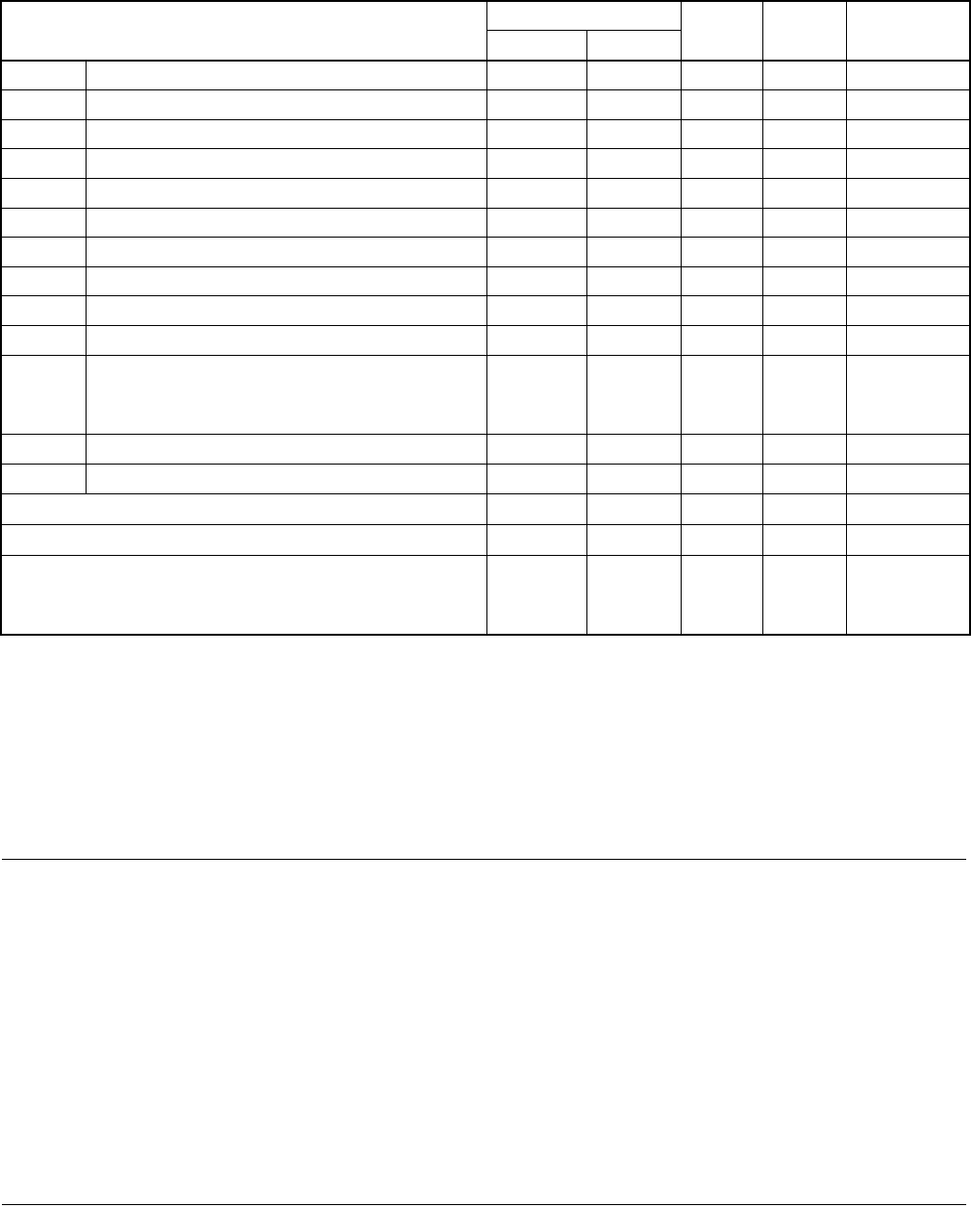

307

*: Use 0x40, 0x41 for the system code when using REALOS/FR.

ICR: This is the register set within the interrupt controller, and it sets the interrupt levels for each interrupt

request. ICR is prepared corresponding to each of the interruption demand.

TBR: It is a register which shows the first address of the vector table for EIT.

The address to which the offset value determined per TBR and EIT factor is added will be the vector

address.

Note:

From address which TBR shows to vector region for EIT region of 1KB

The size per vector is 4 bytes, and the relationship between the vector number and vector address is

expressed as below.

vctadr = TBR + vctofs

= TBR +(3FCH - 4 × vct)

vctadr: Vector Address

vctofs: Vector offset

vct: Vector number

IRQ15

16 bit Timer (Timer0) 31 1F

H

ICR15 0380

H

000FFF80

H

IRQ16 16 bit Timer (Timer 1) 32 20

H

ICR16 037C

H

000FFF7C

H

IRQ17 16 bit Timer (Timer2) 33 21

H

ICR17 0378

H

000FFF78

H

IRQ18 16 bit Timer (Timer3) 34 22

H

ICR18 0374

H

000FFF74

H

IRQ19 Serial ch0(SIO0) 35 23

H

ICR19 0370

H

000FFF70

H

IRQ20 Serial ch1(SIO1) 36 24

H

ICR20 036C

H

000FFF6C

H

IRQ21 Serial ch2(SIO2) 37 25

H

ICR21 0368

H

000FFF68

H

IRQ22 10 bit A/D converter (SOFT) 38 26

H

ICR22 0364

H

000FFF64

H

IRQ23 Key input Interrupt 39 27

H

ICR23 0360

H

000FFF60

H

IRQ24 System reservation

40 28

H

ICR24 035C

H

000FFF5C

H

IRQ25

to

IRQ45

System reservation

41

to

61

29

H

to

3D

H

ICR25

to

ICR45

0358

H

to

0308

H

000FFF58

H

to

000FFF08

H

IRQ46 FLASH

62 3E

H

ICR46 0304

H

000FFF04

H

IRQ47 Delayed Interrupt Factor bit

63 3F

H

ICR47 0300

H

000FFF00

H

System reservation (using for REALOS

*

)

64 40

H

-02FC

H

000FFEFC

H

System reservation (using for REALOS

*

)

65 41

H

-02F8

H

000FFEF8

H

System reservation

66

to

255

42

H

to

FF

H

-

02F4

H

to

0000

H

000FFEF4

H

to

000FFD00

H

Table B-1 Interrupt vector table (Continued)

Interrupt cause

Interrupt Vector number

Interru

pt level

Offset

TBR default

address

10 decimal 16 decimal