298

Appendix A I/O Map

Appendix A I/O Map

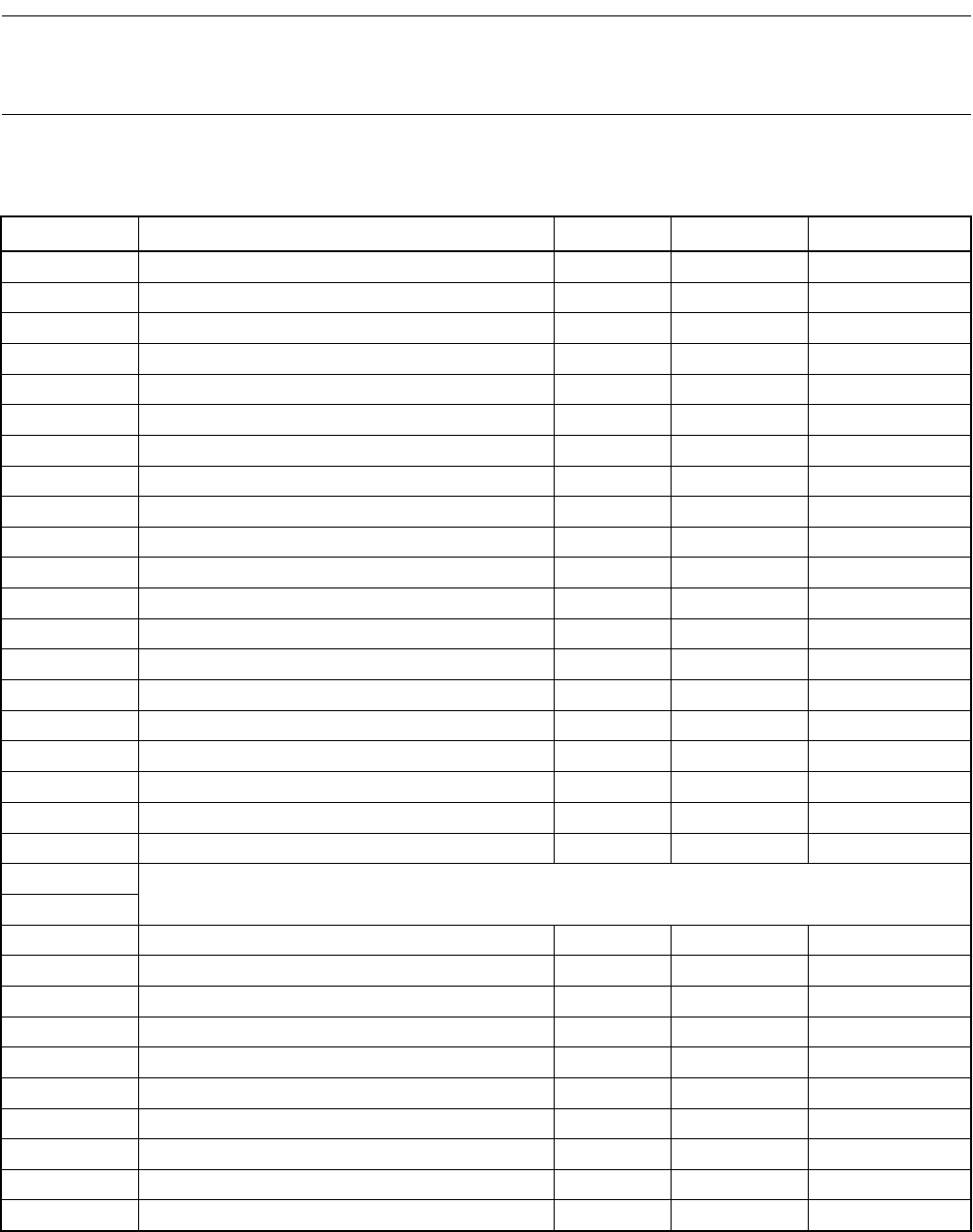

Addresses shown on the Table A-1 are allocated to registers of the peripheral functions

built into the MB91191/MB91192 series.

■

I/O Map

Table A-1 I/O Map

Address Register Name Access Register Initial value

00000

H

Port 3 data register R/W PDR3

XXXX XXXX

B

00001

H

Port 2 data register R/W PDR2

XXXX XXXX

B

00002

H

Port 1 data register R/W PDR1

XXXX XXXX

B

00003

H

Port 0 data register R/W PDR0

XXXX XXXX

B

00004

H

Port 7 data register R/W PDR7

---- ---X

B

00005

H

Port 6 data register R/W PDR6

XXXX XXXX

B

00006

H

Port5 data register R/W PDR5

XXXX XXXX

B

00007

H

Port 4 data register R/W PDR4

XXXX XXXX

B

00008

H

Port 3 data direction register W DDR3

0000 0000

B

00009

H

Port 2 data direction register W DDR2

0000 0000

B

0000A

H

Port 1 data direction register W DDR1

0000 0000

B

0000B

H

Port 0 data direction register W DDR0

0000 0000

B

0000C

H

Port 7 data direction register W DDR7

---- ---0

B

0000D

H

Port 6 data direction register W DDR6

0000 0000

B

0000E

H

Port 5 data direction register W DDR5

0000 0000

B

0000F

H

Port 4 data direction register W DDR4

0000 0000

B

00010

H

Port B data register R/W PDRB

XXXX XXXX

B

00011

H

Port A data register R/W PDRA

XXXX XXXX

B

00012

H

Port 9 data register R/W PDR9

---X XXXX

B

00013

H

Port 8 data register R/W PDR8

XXXX XXXX

B

00014

H

Reserved

00015

H

00016

H

Port D data register R/W PDRD

XXXX XXXX

B

00017

H

Port C data register R/W PDRC

XXXX XXXX

B

00018

H

Port B data direction register W DDRB

0000 0000

B

00019

H

Port A data direction register W DDRA

0000 0000

B

0001A

H

Port 9 data direction register W DDR9

---0 0000

B

0001B

H

Port 8 data direction register W DDR8

0000 0000

B

0001C

H

0001D

H

0001E

H

Port D data direction register W DDRD

0000 0000

B

0001F

H

Port C data direction register W DDRC

0000 0000

B