206

CHAPTER 11 12-bit PWM

11.2 Register of 12-bit PWM

Register configuration/functions of 12-bit PWM is shown.

■ PWMx Control Register (PWMxC)

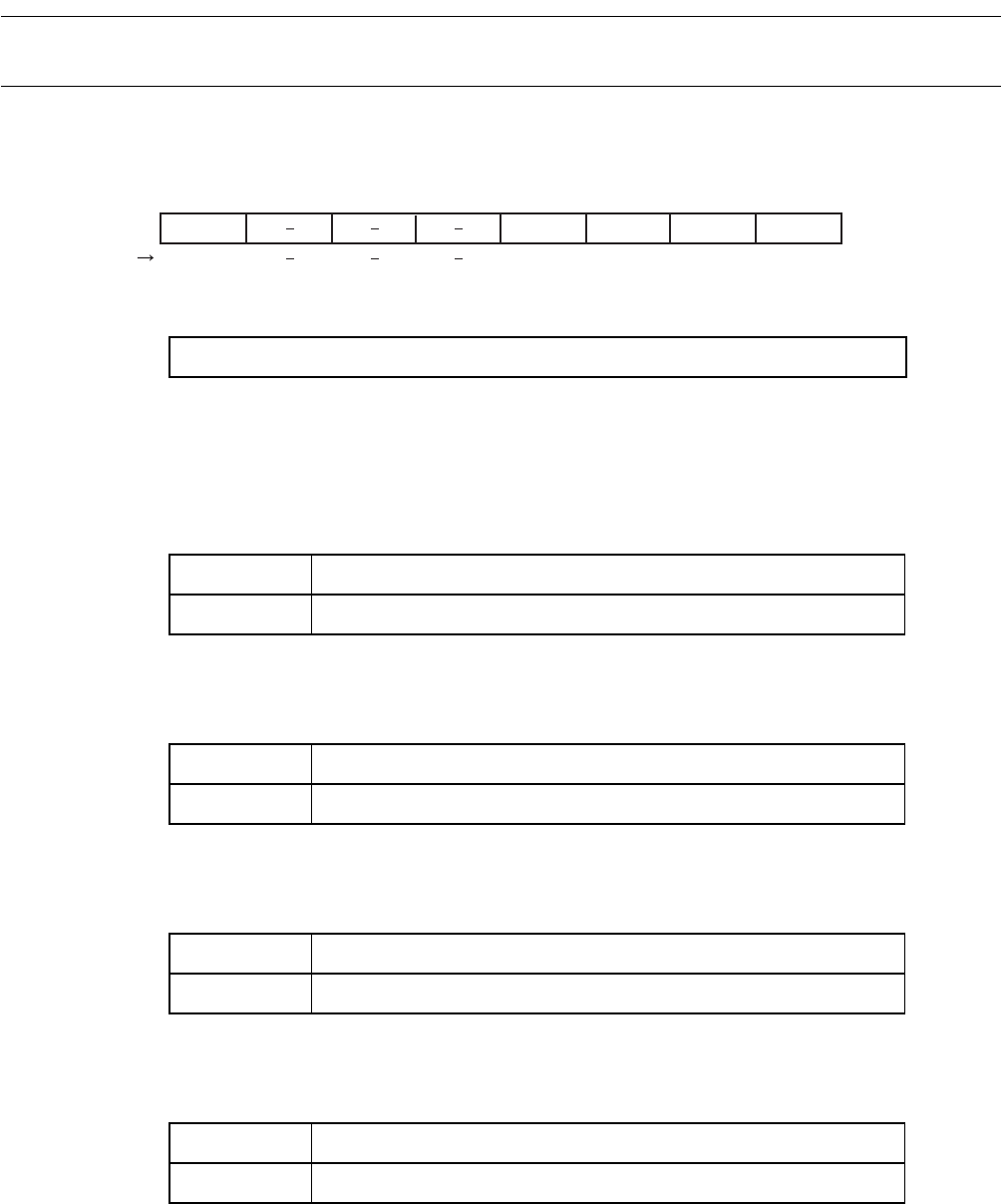

Figure 11.2-1 PWMx Control Register (PWMxC)

[bit7]:Test

[bit6 to 4]:

It is an unused bit.

[bit3]:STR

It is PWM operation enable bit.

[bit2]:CKS

It is clock select bit.

[bit1]:LFLG

It is load request flag to compare latch.

[bit0]:LREQ

It is load request bit.

The read value of this bit is always "0".

7 6 5 4 3 2 1 0

0--- 00X0

B

Initial value

bit

R/W R/W R/W R W

Test STR CKS LFLG LREQ

Access

Please set "0".

0 Operation disabled

1 Operation enabled

0 1/fch (fch: 50 ns in @20 MHz)

1 2/fch (fch: 100 ns in @20 MHz)

0 No load request and complete load.

1 Load request

0 None

1 Load data register value to compare latch.