259

■

Interrupt Function

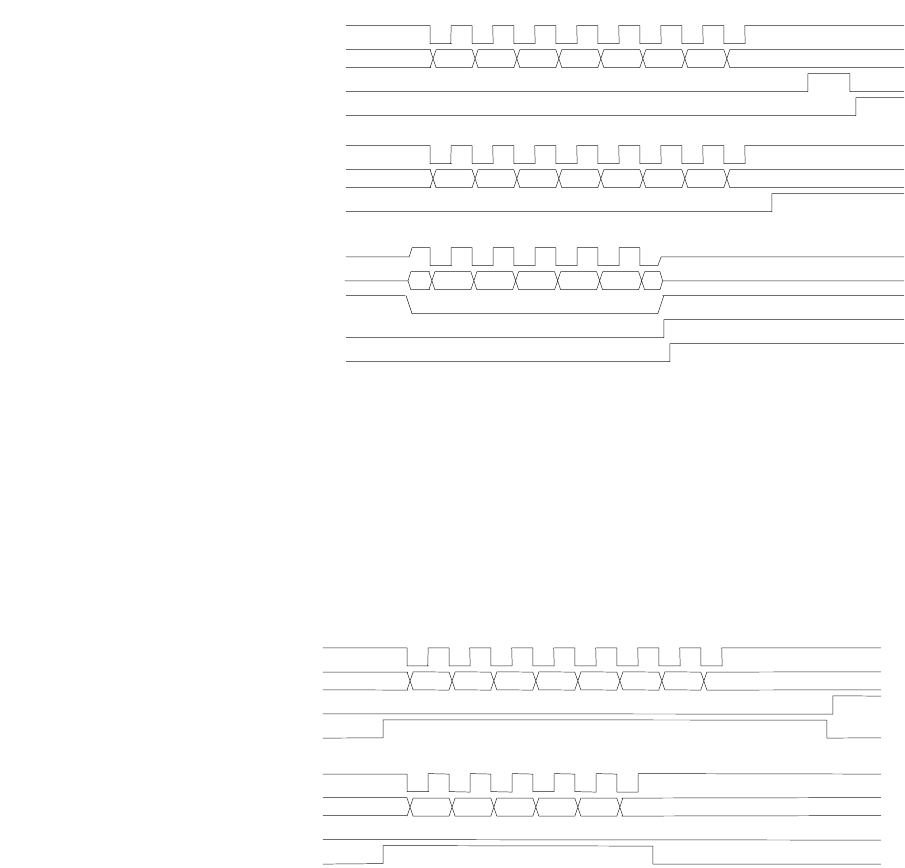

The serial I/O is set by the transfer end flag (SIF) bit when data transfer ends. In this case, the interrupt

request is generated. When termination (suspension) is executed by inputting chip select, the chip select

termination flag (CSAF) bit is set and an interrupt request is generated.

Figure 17.4-6 Interrupt generation timing

■

Start/Stop Timing of Shift Operation

Writing "1" to the ST bit of the SCR initiates transfer, whereas writing "0" stops transfer. (When XCS input

is enabled, transfer does not start until the falling of the XCS pin is detected after writing "1" to the ST bit.)

When data transfer ends, clears the ST bit automatically to "0" and stops operation.

●

Internal shift clock mode

Figure 17.4-7 Shift operation start/stop timing

Internal Clock Mode 1 byte Transmission

Transfer End Interruption

#0 #1 #2 #3 #4 #5 #6 #7

#0 #1 #2 #3 #4 #5 #6 #7

#0 #1 #2 #3 #4

INT-REQ

CSAF

XCS

SO

SCK

(INT-REQ)SIF

SO

SCK

STB

SO

SCK

(INT-REQ)SIF

External Clock Mode 1 byte Transmission

Transfer End Interruption

Internal Clock Mode 1 byte Transmission

Forced End Interruption of XCS

At 1 byte Transmission end

#0 #1 #2 #3 #4 #5 #6 #7

#0 #1 #2 #3 #4 #5

ST

SIF

SO

SCK

SIF

SO

SCK

ST

At 1 byte Transmission suspend