27

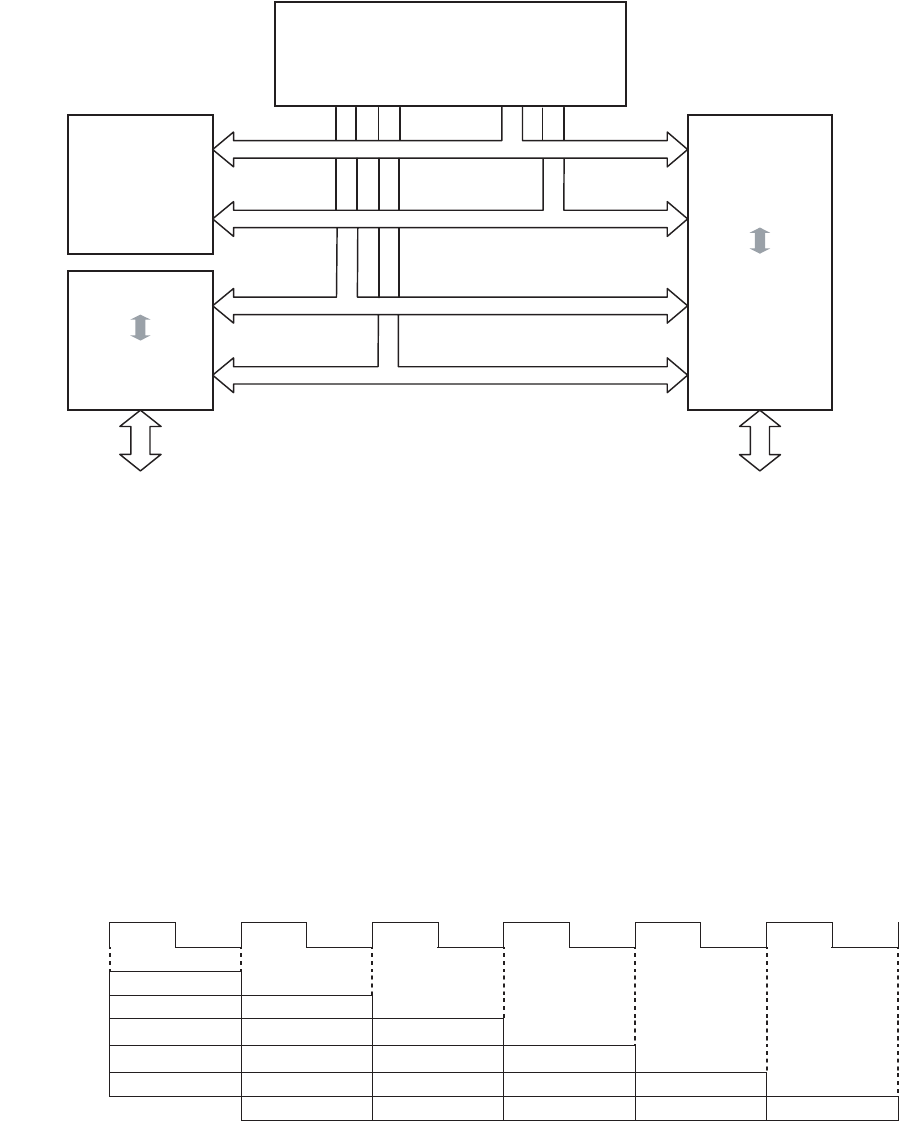

Figure 3.2-1 shows the construction of internal architecture.

Figure 3.2-1 Construction of Internal architecture

●

CPU

The FR20's 32-bit RISC architecture is compactly implemented on the CPU. A five-level command

pipeline method is adopted to execute one command per cycle. The pipeline is composed of the following

stages.

• Instruction fetch (IF): The instruction address is output, and the instruction is fetched.

• Instruction decode (ID): The decode does the fetched instruction. The register is read.

• Execution (EX): The operation is executed.

• Memory access (MA): Loading into the memory or the store is accessed.

• Write-back (WB): Writes the operation results (or loaded memory data) to the register.

Figure 3.2-2 shows the instruction pipeline.

Figure 3.2-2 Instruction pipeline

The instruction is never in any order executed. Accordingly, if command A enters the pipeline before

command B, command A always reaches write backstage before command B.

As a rule, the instruction is executed at the speed of one instruction per cycle. However, a number of cycles

D-BUS I-BUS

R-bus C-bus

FR20 CPU

Instruction

Cache

32bit

16bit

Bus converter

Harvard

Princeton

Bus converter

Bus controller

Resource

CLK

Instruction 1 WB

Instruction 2 MA

Instruction 3 EX

Instruction 4 ID

Instruction 5 IF

Instruction 6

WB

MA

EX

ID

IF

WB

MA

EX

ID

WB

MA

EX

WB

MA

WB